#### THESIS / UNIVERSITÉ DE BRETAGNE OCCIDENTALE

under the seal of the Université Européenne de Bretagne

for the title of

DOCTOR of the UNIVERSITÉ DE BRETAGNE OCCIDENTALE

Distinction: Science and Technology of Information and Communication

École Doctorale Santé, Information, Communication,

Mathématique, Matière

presented by

# Shuai Li

Prepared at Laboratoire des Sciences et Techniques de l'Information, de la Communication et de la Connaissance and Thales Communications & Security

Scheduling Analysis of Tasks Constrained by Time-Division Multiplexing: Application to Software Radio Protocols

#### Thesis defended on Novembre 27th 2014

In front of the following committee:

#### Frédéric BONIOL

Professor, Université de Toulouse, ONERA / referee

#### Michel BOURDELLÈS

Doctor, Thales Communications & Security / guest

#### **Maryline CHETTO**

Professor, Université de Nantes, IRCCyN / referee

#### Éric GRESSIER-SOUDAN

Professor, Conservatoire National des Arts et Métiers, CEDRIC / examiner

#### Stéphane RUBINI

Associate Professor, Université de Bretagne Occidentale, Lab-STICC / examiner

#### José RUFINO

Associate Professor, Universidade de Lisboa / examiner

#### Frank SINGHOFF

Professor, Université de Bretagne Occidentale, Lab-STICC / examiner

# **ACKNOWLEDGMENTS**

I present my thanks to Frédéric Boniol and Maryline Chetto for taking their time to review my dissertation. It was an honor to have you as referees. I also thank Éric Gressier-Soudan and José Rufino for honoring me by accepting to be examiners of my dissertation.

I would like to thank my doctoral director Frank Singhoff for his outstanding commitment to this work. I thank him for always being available and helpful. His knowledge, insight, and advices improved immensely the quality of the scientific and technical contributions of this work, but also its presentation. I thank him for his guidance, which helped me gain invaluable skills as a researcher. I would also like to thank Michel Bourdellès and Stéphane Rubini for supervising my doctoral thesis. I thank them for the time they took to evaluate my contributions, the problems they noticed, and the discussions we had, which helped me progress in my work and results.

The opportunity to work on this doctoral project was offered by Thales Communications & Security, the Lab-STICC laboratory, and the Université de Bretagne Occidentale. I would especially like to thank Yves-André Caparros, Marc Isard, and Pierre Verrecchia, from Thales Communications & Security, for allowing me to participate in their research projects and base my contributions on problems encountered in real case-studies developed at Thales.

My thanks also go to all of my colleagues. Not only were our technical discussions very interesting, but it was wonderful to work with you everyday. In particular, I would like thank Brigitte D., Bruno C., Christian F., Claire G., Émilie O., Grégory G., Jean-Philippe B., Josselyn K., Julien M., Laurent P., Martin B., Méziane O., Mounir L., Thierry C., Véronique K., Vincent G., Xavier R.

Last, but not least, I would like to thank my family, my friends, and my special someone, who helped me with the review of this dissertation and supported me during these years.

Abstract Résumé

The work, presented in this thesis, aims at performing automatically scheduling analysis of Time Division Multiple Access (TDMA) based communication systems. Products called software radio protocols, developed at Thales Communications & Security, are examples of such systems.

TDMA is a channel access method based on the division of time into several time slots. TDMA-based software radio protocols are real-time embedded systems. They are implemented by tasks that are statically allocated on multiple processors. A task may have an execution time, a deadline, and a release time that depend on TDMA. The tasks also have dependencies through precedence and shared resources.

TDMA-based software radio protocols have architecture characteristics that are not handled by scheduling analysis methods of the literature. A consequence is that existing methods give either optimistic or pessimistic analysis results. Furthermore, existing architecture models at Thales do not contain enough information to be used for scheduling analysis. The information is only available in specification documents. These issues impact the possibility to perform scheduling analysis, but also the possibility to perform it automatically.

The propositions of this thesis solve these problems. An experimental architecture model is proposed in the UML MARTE modeling language. The architecture model is transformed to a task model called Dependent General Multiframe (DGMF). The DGMF task model describes, in particular, the different jobs of a task, and task dependencies. To analyze DGMF tasks, they are transformed to another model called tree-shaped transaction. Transactions are precedence dependent tasks. Transactions that result from the transformation have non-immediate tasks. These tasks are not necessarily released immediately by their predecessor task. To consider the effects of non-immediateness, this thesis proposes the WCDOPS+NIM schedulability test for tree-shaped transactions. The general analysis method is implemented as a toolchain that can be used by engineers at Thales.

Experimental results show that the propositions give less pessimistic schedulability results, compared to fundamental methods. The results are less pessimistic for both randomly generated systems and real case-studies from Thales. Furthermore, experiments show that scheduling analysis can be applied automatically to a TDMA-based software radio protocol.

Less pessimistic results are important for engineering work, in order to limit the over-dimensioning of resources. The automatic analysis is a gain in productivity. These are advantages for engineers in the more and more competitive market of software radios.

Le travail présenté dans cette thèse vise à analyser automatiquement l'ordonnancement de systèmes de communications basés sur TDMA. Des produits développés chez Thales Communications & Security, appelés protocoles radio logicielle, sont des exemples de tels systèmes.

TDMA est une méthode d'accès au canal basée sur la division du temps en slot temporel. Les protocoles radio logicielle basés sur TDMA sont des systèmes temps-réel embarqués. Ils sont implémentés avec des tâches allouées statiquement sur des processeurs. Une tâche peut avoir un temps d'exécution, une échéance, et un temps d'activation qui dépendent de TDMA. Les tâches sont dépendantes par précédence et ressource partagée.

Les protocoles radio logicielle basé sur TDMA ont des caractéristiques d'architecture qui ne sont pas supportés par les méthodes d'analyse de la littérature. Elles donnent donc des résultats d'analyse optimistes ou pessimistes. De plus, les modèles d'architecture à Thales ne contiennent pas assez d'informations pour être utilisés pour l'analyse. Ces informations ne sont disponibles que dans des documents de spécification. Ces problèmes impactent la possibilité d'appliquer l'analyse mais aussi de l'appliquer automatiquement.

Les propositions de cette thèse règlent ces problèmes. Un modèle d'architecture expérimental est proposé en UML MARTE. Le modèle d'architecture est transformé au modèle de tâche Dependent General Multiframe (DGMF). DGMF décrit, en particulier, les activations d'une tâche et ses dépendances. Pour analyser les tâches DGMF, elles sont transformées en un autre modèle appelé transaction arborescente. Les transactions sont des tâches contraintes par précédence. Les transactions issues de la transformation ont des tâches nonimmédiates. Une telle tâche n'est pas nécessairement activée immédiatement par son prédécesseur. Pour prendre en compte l'effet de la non-immédiateté, cette thèse propose le test d'ordonnançabilité WCDOPS+NIM pour transaction arborescente. La méthode d'analyse générale est implémentée comme chaîne d'outils dédiée aux ingénieurs chez Thales.

Des expériences montrent que les propositions donnent des résultats d'ordonnançabilité moins pessimistes, comparés aux méthodes fondamentales. Les résultats sont moins pessimistes pour des systèmes générés aléatoirement et des vrais cas d'étude chez Thales. L'analyse peut aussi être appliquée automatiquement à un protocole radio logicielle basé sur TDMA.

Des résultats moins pessimistes permettent de limiter le surdimensionnement des ressources. L'analyse automatique est un gain de productivité. Ce sont des avantages pour les ingénieurs dans un marché de la radio logicielle de plus en plus compétitif.

# CONTENTS

| In | trodu      | action                                                              | 1  |

|----|------------|---------------------------------------------------------------------|----|

| i  | STAT       | TE OF THE ART                                                       | 7  |

| 1  | REA        | AL-TIME EMBEDDED SYSTEM                                             | 9  |

|    | 1.1        | Generalities on Real-Time Embedded Systems                          | 9  |

|    | 1.2        | Software of a RTES                                                  | 10 |

|    |            | 1.2.1 Concept of Task                                               | 10 |

|    |            | 1.2.2 Types of Task                                                 | 11 |

|    |            | 1.2.3 Parameters of Task                                            | 12 |

|    |            | 1.2.4 Task Dependencies                                             | 13 |

|    |            | 1.2.5 Memory Partition                                              | 13 |

|    | 1.3        | Operating System of a RTES                                          | 14 |

|    | 1.5        | 1.3.1 Scheduler                                                     | 14 |

|    |            | 1.3.2 Resource Synchronization Primitive                            | 17 |

|    | 1.4        | Hardware of a RTES                                                  | 19 |

|    | 1.4        | 1.4.1 Scheduling and Processors                                     | 19 |

|    |            | 1.4.2 Scheduling and Networks                                       | 20 |

|    | 1.5        | Development Cycle                                                   | 20 |

|    | 1.6        | Model-Driven Engineering                                            | 21 |

|    | 1.0        | 1.6.1 Introduction to Models                                        |    |

|    |            | 1.6.2 Model Transformation                                          | 21 |

|    | 1 7        | Architecture Description Languages                                  | 22 |

|    | 1.7        |                                                                     | 22 |

|    |            | ·                                                                   | 23 |

|    | <i>-</i> 0 | 1.7.2 RTES Domain-Specific Architecture Description Languages       | 27 |

|    | 1.8        | Conclusion                                                          | 29 |

| 2  |            | HEDULING ANALYSIS                                                   | 31 |

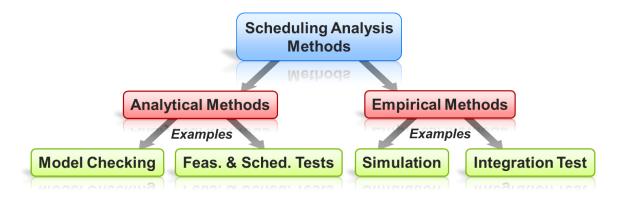

|    | 2.1        | Methods of Scheduling Analysis                                      | 31 |

|    |            | 2.1.1 Empirical Methods                                             | 32 |

|    |            | 2.1.2 Analytical Methods                                            | 32 |

|    | 2.2        | Task Models and Tests                                               | 33 |

|    | 2.3        | Fundamental Models: Periodic and Sporadic                           | 35 |

|    |            | 2.3.1 Definition                                                    | 35 |

|    |            | 2.3.2 Processor Utilization Feasibility Tests                       | 36 |

|    |            | 2.3.3 Response Time Schedulability Test                             | 37 |

|    |            | 2.3.4 Processor Demand Feasibility Tests                            | 40 |

|    | 2.4        | Transaction Models: Illustration with Tree-Shaped                   | 41 |

|    |            | 2.4.1 Definition                                                    | 41 |

|    |            | 2.4.2 Offset-Based Response Time Analysis: A Historical Perspective | 43 |

|    |            | 2.4.3 Basic Concepts of RTA of Transactions                         | 46 |

|    |            | 2.4.4 The WCDOPS+ Test                                              | 50 |

|    | 2.5        | Multiframe Models: Illustration with GMF                            | 62 |

|    | -          | 2.5.1 Definition                                                    | 62 |

|    |            | 2.5.2 Processor Demand Feasibility Test                             | 63 |

|    |            | 2.5.3 Response Time Schedulability Test                             | 64 |

|    | 2.6        | DAG Task Models: Illustration with Sporadic DAG Task                | 65 |

|    |      | 2.6.1        | Definition                                                                 | 65  |

|----|------|--------------|----------------------------------------------------------------------------|-----|

|    |      | 2.6.2        | Generalizations Between DAG Task Models                                    | 66  |

|    |      | 2.6.3        | Speedup Bound Feasibility Tests                                            | 66  |

|    |      | 2.6.4        | Schedulability Tests                                                       | 67  |

|    | 2.7  | Concl        | usion                                                                      | 67  |

| 3  | SCH  | EDULI        | NG ANALYSIS OF SOFTWARE RADIO PROTOCOL                                     | 69  |

| )  | 3.1  |              | luction to Radios                                                          | 69  |

|    | J. 2 | 3.1.1        | Radio Network                                                              | 70  |

|    |      | 3.1.2        | Radio Protocol Stack                                                       | 70  |

|    |      | 3.1.3        | Impact of TDMA on Radio Protocol Stack                                     |     |

|    |      | 3.1.4        | From Application Constraints and Radio Protocol Configuration to Task Con- | 71  |

|    |      | 3.1.4        | straints                                                                   |     |

|    | 2.2  | Conto        | ext of Work                                                                | 73  |

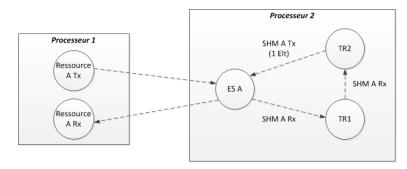

|    | 3.2  |              | Software and Execution Platform Architecture                               | 74  |

|    |      | 3.2.1        |                                                                            | 74  |

|    |      | 3.2.2        | Type of Software Architecture of a Software Radio Protocol                 | 76  |

|    |      | 3.2.3        | Summary of Characteristics for Scheduling Analysis                         | 76  |

|    |      | 3.2.4        | Software Radio Protocol Development                                        | 78  |

|    | 3.3  |              | em Statement                                                               | 78  |

|    |      | 3.3.1        | Applicability of Task Models                                               | 78  |

|    |      | 3.3.2        | Availability of Analysis Methods Implemented in Tools                      | 80  |

|    |      | 3.3.3        | Applicability of ADLs                                                      | 81  |

|    |      | 3.3.4        | Summary of Problem Statement                                               | 82  |

|    | 3.4  | Overv        | view of the Solution                                                       | 82  |

|    |      | 3.4.1        | Applicability of Task Models Problem                                       | 83  |

|    |      | 3.4.2        | Availability of Analysis Methods Implemented in Tools Problem              | 84  |

|    |      | 3.4.3        | Applicability of ADLs Problem                                              | 84  |

|    | 3.5  | Concl        | usion                                                                      | 86  |

|    |      |              |                                                                            |     |

| ii | CON  | NTRIBU       | UTIONS                                                                     | 87  |

| 4  | EXP  |              | NT ON SCHEDULING ANALYSIS OF SOFTWARE RADIO PROTOCOL                       | 89  |

|    | 4.1  |              | Study of the Experiment                                                    | 89  |

|    | 4.2  | Apply        | ring the Periodic Task Model                                               | 91  |

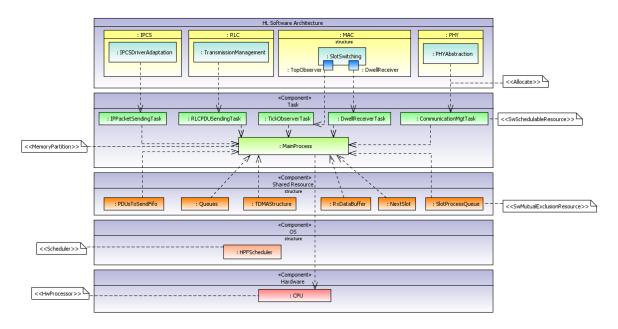

|    |      | 4.2.1        | High Level Software Architecture Model                                     | 93  |

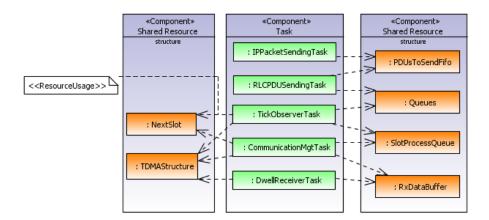

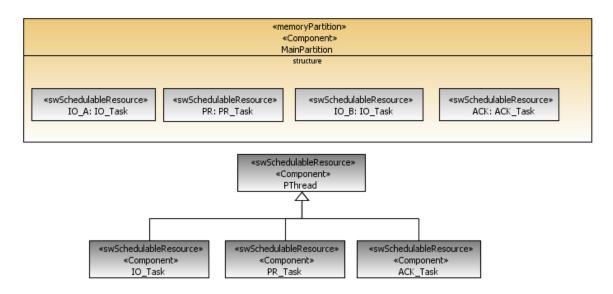

|    |      | 4.2.2        | Software and Execution Platform Architecture Model                         | 95  |

|    |      | 4.2.3        | Associations Between Entities                                              | 96  |

|    |      | 4.2.4        | Transformation to Cheddar                                                  | 98  |

|    | 4.3  | Discu        | ssion on the Analysis Results                                              | 98  |

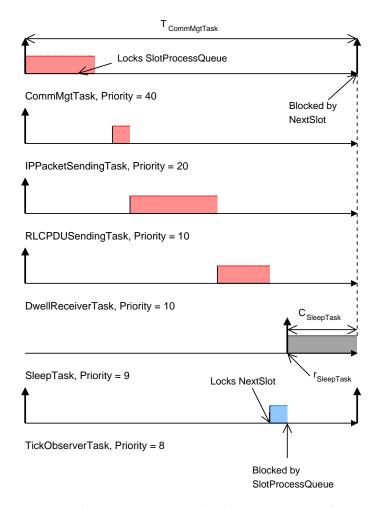

|    |      | 4.3.1        | Software Design Mistake                                                    | 98  |

|    |      | 4.3.2        | Missed Deadline                                                            | 101 |

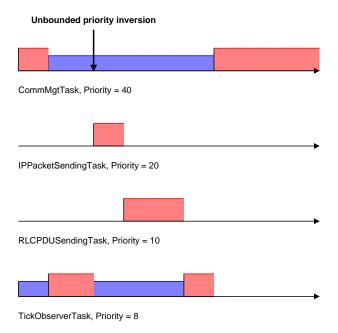

|    |      | 4.3.3        | Unbounded Priority Inversion                                               | 101 |

|    |      | 4.3.4        | Pessimistic WCRTs                                                          | 102 |

|    |      | 4.3.5        | 71 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                     | 103 |

|    |      | 4.3.6        | Summary of the Analysis Results                                            |     |

|    | 4.4  |              | usion                                                                      |     |

| _  |      |              | ODEL FOR SOFTWARE RADIO PROTOCOLS                                          | 105 |

| 5  |      |              | ndent General Multiframe                                                   | _   |

|    | 5.1  | •            |                                                                            | -   |

|    |      | 5.1.1        | DGMF Definitions and Properties                                            | -   |

|    |      | 5.1.2        | DGMF Example                                                               | -   |

|    |      | 5.1.3<br>DCM | Applicability of GMF Analysis Methods on DGMF                              |     |

|    | 5.2  |              | F Scheduling Analysis Using Transactions                                   |     |

|    |      | 5.2.1        | Transaction Reminder and New Definitions                                   |     |

|    |      | 5.2.2        | DGMF To Transaction                                                        | 111 |

|     |       | 5.2.3         | Transformation Example                                         |     |

|-----|-------|---------------|----------------------------------------------------------------|-----|

|     |       | 5.2.4         | Assessing Schedulability of Resulting Transactions             |     |

|     | 5.3   |               | nary of DGMF Analysis Method                                   |     |

|     | 5.4   | Imple         | mentation in Cheddar                                           | -   |

|     |       | 5.4.1         | Cheddar                                                        | -   |

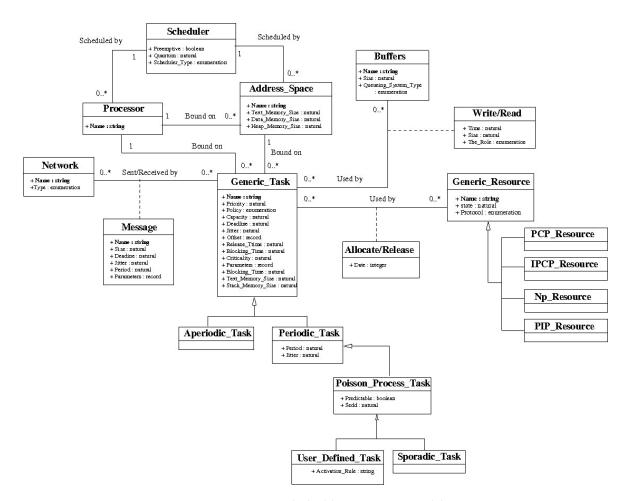

|     |       | 5.4.2         | Implementation of DGMF and Transaction                         |     |

|     |       | 5.4.3         | Discussion on Implementation                                   |     |

|     | 5.5   | Experi        | iment and Evaluation                                           | _   |

|     |       | 5.5.1         | Transformation Correctness                                     | 123 |

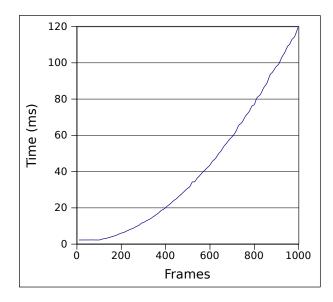

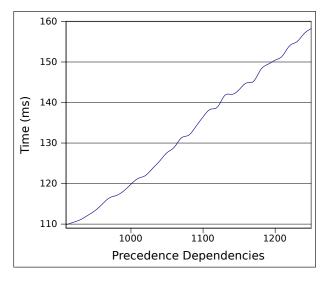

|     |       | 5.5.2         | Transformation Time Performance                                | 126 |

|     |       | 5.5.3         | Case-Study Modeling with DGMF                                  | 127 |

|     | 5.6   | Concl         | usion                                                          | 129 |

| 6   | SCH   | EDULA         | BILITY ANALYSIS OF TREE-SHAPED TRANSACTIONS WITH NON-IMMEDIATE |     |

|     | TAS   | KS            |                                                                | 131 |

|     | 6.1   | Applie        | cability of WCDOPS+ on Non-immediate Tasks                     | 131 |

|     | 6.2   |               | edulability Test for Non-Immediate Tasks                       |     |

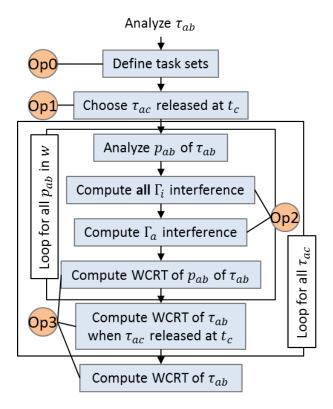

|     |       | 6.2.1         | Overview of the RTA Method                                     |     |

|     |       | 6.2.2         | Opo: Task Sets and Execution Conflicts                         |     |

|     |       | 6.2.3         | Op1: Worst Case Scenario                                       |     |

|     |       | 6.2.4         | Op2: Worst Case Interference                                   |     |

|     |       | 6.2.5         | Op2 cont.: Worst Case Interference Algorithms                  |     |

|     |       | 6.2.6         | Op3: Worst Case Response Time                                  |     |

|     | 6.3   |               | iment and Evaluation                                           |     |

|     | 0.5   |               | WCDOPS+NIM Evaluation                                          |     |

|     |       | 6.3.2         | Experimentation on Software Radio Protocol                     |     |

|     | 6.4   | ,             | usion                                                          |     |

| 7   | •     |               | TECTURE MODEL FOR AUTOMATIC SCHEDULING ANALYSIS                | 151 |

| /   |       |               | iting Specification Documents                                  |     |

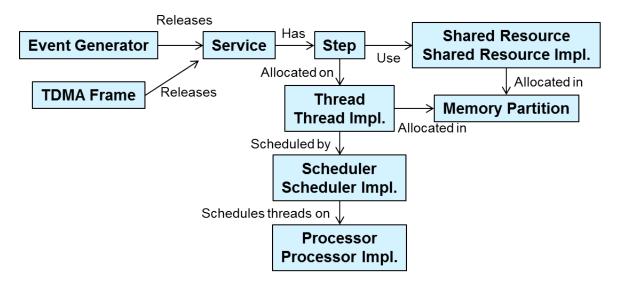

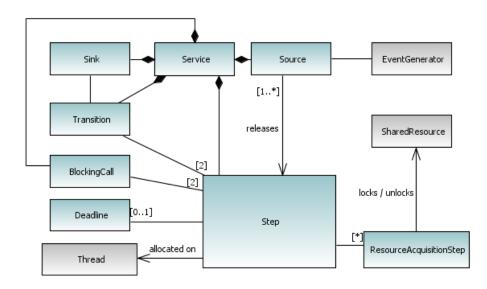

|     | 7.1   |               | Model for Scheduling Analysis: Service Model                   |     |

|     | 7.2   |               | Service Model Overview                                         |     |

|     |       | 7.2.1         |                                                                | -   |

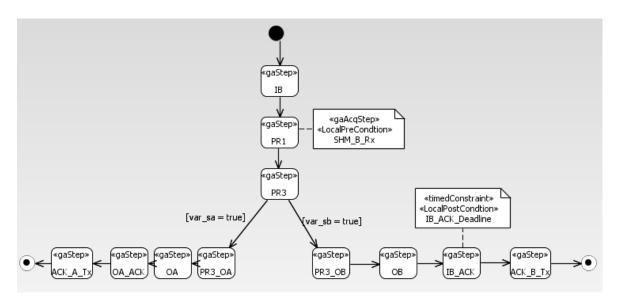

|     |       | 7.2.2         | Service Behavior View                                          |     |

|     |       | 7.2.3         | Event Generator View                                           | _   |

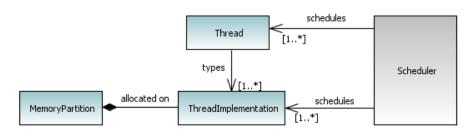

|     |       | 7.2.4         | Thread Implementation View                                     |     |

|     | 7.3   |               | re to Cheddar                                                  | 159 |

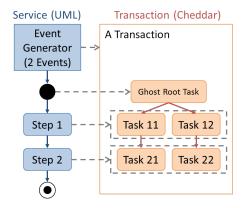

|     |       | 7.3.1         | Overview of the Transformation                                 |     |

|     |       | 7.3.2         | Algorithm Overview                                             |     |

|     | 7.4   | •             | iment and Evaluation                                           |     |

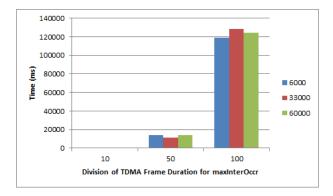

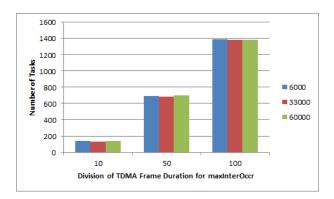

|     |       | 7.4.1         | Simulation Setup                                               |     |

|     |       | 7.4.2         | Results                                                        |     |

|     | 7.5   | Concl         | usion                                                          | 164 |

| Co  | nclus | sion          |                                                                | 165 |

|     |       |               |                                                                | _   |

| 111 |       | PENDIX        |                                                                | 169 |

| A   | CHE   | DDAR-         | ADL                                                            | 171 |

| В   | COM   | <b>IPLETE</b> | SOFTWARE RADIO PROTOCOL CASE-STUDY                             | 173 |

| C   | SER   | VICE M        | ODEL                                                           | 175 |

|     | C.1   | Servic        |                                                                | 175 |

|     |       | C.1.1         | Entities                                                       | 175 |

|     |       | C.1.2         | Mapping to MARTE                                               | 175 |

|     |       | C.1.3         | Diagram Palette                                                | 175 |

|     | C 2   | Sorvio        | e Behavior View                                                | 100 |

|    |      | c.2.1 Entities                       | 175 |

|----|------|--------------------------------------|-----|

|    |      | c.2.2 Mapping to MARTE               | 175 |

|    |      | c.2.3 Diagram Palette                | 178 |

|    | C.3  | Event Generator View                 | 178 |

|    | C.4  | Thread Implementation View           | 178 |

|    |      | c.4.1 Entities                       | 178 |

|    |      | c.4.2 Mapping to MARTE               | 181 |

|    |      | c.4.3 Diagram Palette                | 181 |

|    | C.5  | Shared Resource Implementation View  | 182 |

|    |      | c.5.1 Entities                       | 182 |

|    |      | c.5.2 Mapping to MARTE               | 182 |

|    |      | c.5.3 Diagram Palette                | 182 |

|    | c.6  | Operating System Implementation View | 184 |

|    |      | c.6.1 Entities                       | 184 |

|    |      | c.6.2 Mapping to MARTE               | 184 |

|    |      | c.6.3 Diagram Palette                | 184 |

|    | C.7  | Hardware Implementation View         | 184 |

|    |      | c.7.1 Entities                       | 184 |

|    |      | c.7.2 Mapping to MARTE               | 184 |

|    |      | c.7.3 Diagram Palette                | 186 |

| D  | SER  | VICE TO CHEDDAR                      | 187 |

|    | D.1  | Main Program                         | 187 |

|    | D.2  | Node Processing                      | 188 |

|    | D.3  | Step Processing                      | 189 |

|    | D.4  | Thread Processing                    | 189 |

|    | D.5  | Scheduler and Processor Processing   | 191 |

|    | D.6  | Partition Processing                 | 191 |

|    | D.7  | Resource Acquisition Processing      | 192 |

|    | D.8  | Shared Resource Processing           | 192 |

|    |      |                                      |     |

| BI | BLIO | GRAPHY                               | 195 |

# LIST OF FIGURES

| Figure 1.1  | RTES Architecture                                                         | 10  |

|-------------|---------------------------------------------------------------------------|-----|

| Figure 1.2  | Task Life Cycle                                                           | 11  |

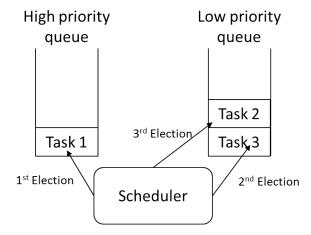

| Figure 1.3  | Scheduler Electing Tasks in Queues                                        | 15  |

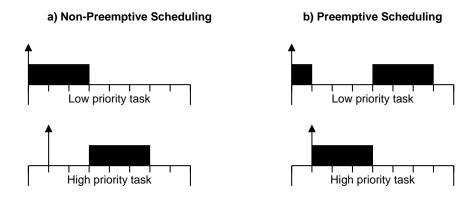

| Figure 1.4  | Preemptive vs Non-Preemptive Scheduling                                   | 16  |

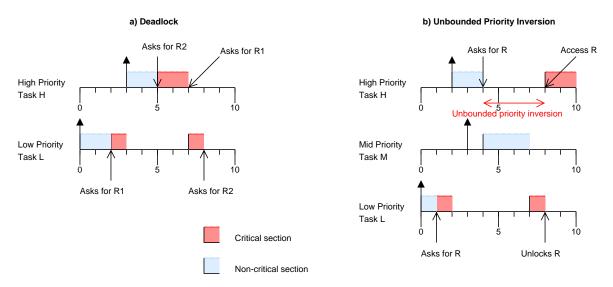

| Figure 1.5  | Deadlock and Unbounded Priority Inversion Example                         | 18  |

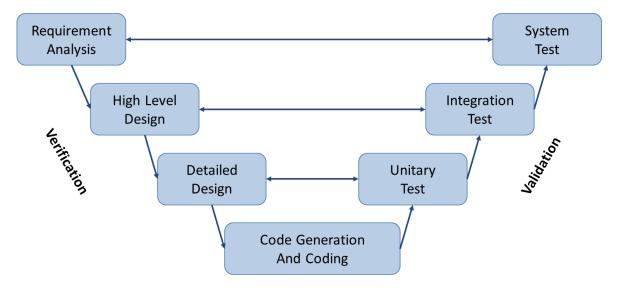

| Figure 1.6  | V-Model Development Cycle                                                 | 20  |

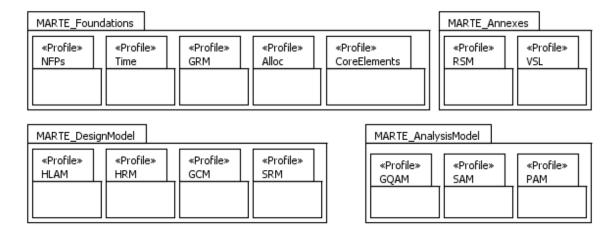

| Figure 1.7  | MARTE Packages                                                            | 25  |

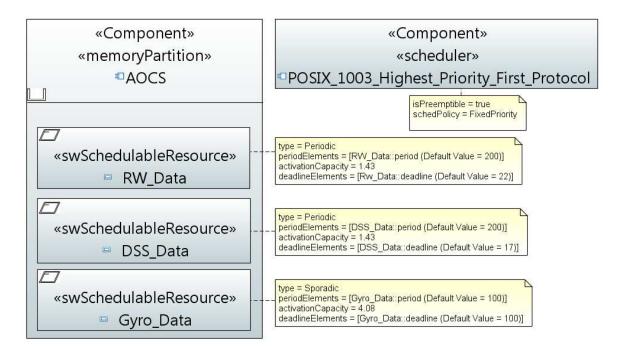

| Figure 1.8  | Example of Using of MARTE                                                 | 26  |

| Figure 1.9  | Component-Based Model                                                     | 28  |

| Figure 1.10 | MyCCM Code Generation                                                     | 28  |

| Figure 2.1  | Scheduling Analysis Methods                                               | 31  |

| Figure 2.2  | Task Models                                                               | 34  |

| Figure 2.3  | Distributed System                                                        | 41  |

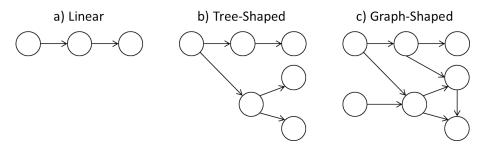

| Figure 2.4  | Transaction Types                                                         | 43  |

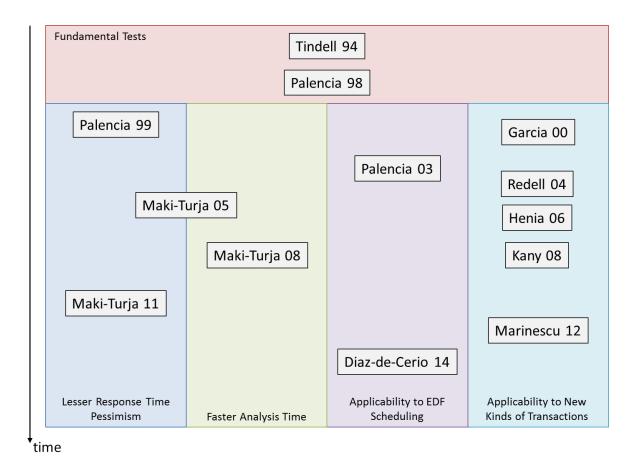

| Figure 2.5  | Schedulability Tests Based on RTA for Transactions                        | 44  |

| Figure 2.6  | Transactions and Interference                                             | 47  |

| Figure 2.7  | WCDOPS+ Overview: Circles indicate key operations                         | 51  |

| Figure 2.8  | Tree-Shaped Transaction                                                   | 52  |

| Figure 2.9  | GMF Example                                                               | 63  |

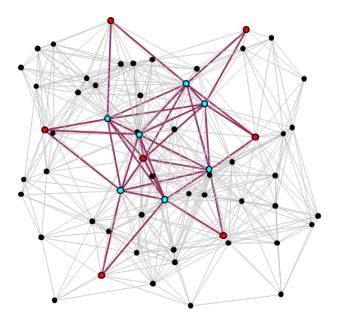

| Figure 3.1  | Wireless Ad-hoc Network                                                   | 70  |

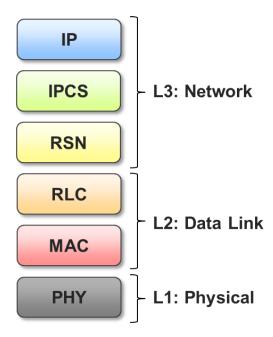

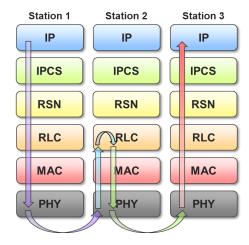

| Figure 3.2  | Protocol Stack                                                            | 71  |

| Figure 3.3  | TDMA Frame                                                                | 72  |

| Figure 3.4  | TDMA Frame Modes                                                          | 72  |

| Figure 3.5  | Radio Network with QoS Constraints                                        | 73  |

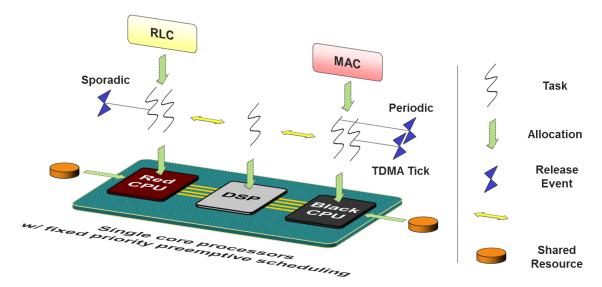

| Figure 3.6  | Execution Environment of a Software Radio Protocol                        | 74  |

| Figure 3.7  | Architecture for Scheduling Analysis                                      | 75  |

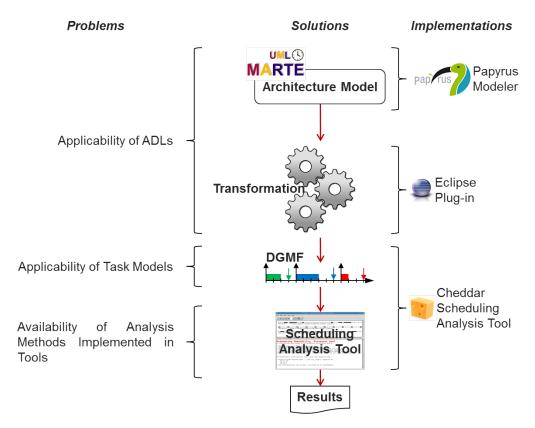

| Figure 3.8  | Overview of the Solution                                                  | 83  |

| Figure 4.1  | Communicating HDRN Layers                                                 | 90  |

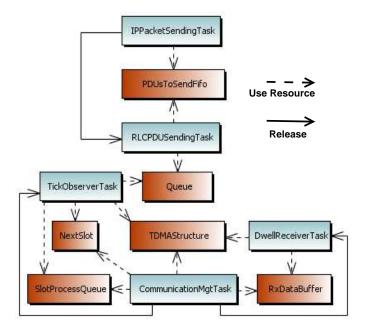

| Figure 4.2  | HDRN Tasks and Shared Resources                                           | 91  |

| Figure 4.3  | Experiment Setup                                                          | 92  |

| Figure 4.4  | Applied GCM and HLAM Stereotypes                                          | 93  |

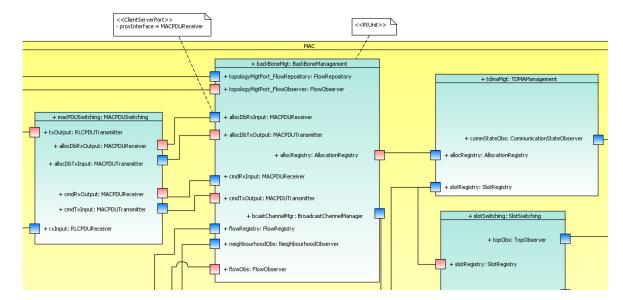

| Figure 4.5  | MAC Layer Model                                                           | 94  |

| Figure 4.6  | Applied GRM, SRM, and HRM Stereotypes                                     | 95  |

| Figure 4.7  | Spatial Distribution View                                                 | 96  |

| Figure 4.8  | Shared Resource Usage View: Dashed arrows are resource usages; For read-  |     |

| 0 1         | ability, not all stereotypes are visible and stereotypes are shown by UML |     |

|             | comments                                                                  | 97  |

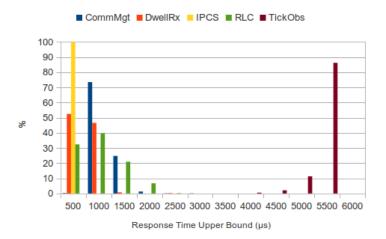

| Figure 4.9  | Measured Response Times of HDRN Tasks                                     | 99  |

| Figure 4.10 | Software Design Mistake                                                   | 100 |

| Figure 4.11 | Unbounded Priority Inversion                                              | 102 |

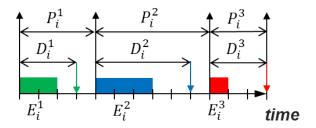

| Figure 5.1  | Example of Schedule of DGMF Tasks                                         | 108 |

| Figure 5.2  | Illustration of DGMF Example for GMF Test                                 | 109 |

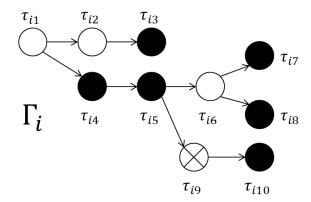

| Figure 5.3  | Tasks Precedence Dependency Graph                                         |     |

| Figure 5.4  | Transaction from DGMF Tasks Transformation                                |     |

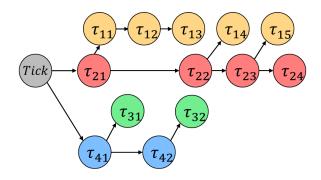

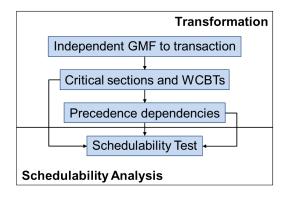

| Figure 5.5  | Summary of Analysis Method                                                | 110 |

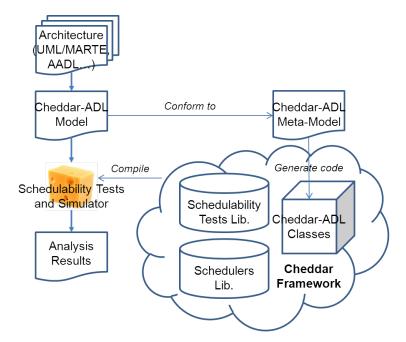

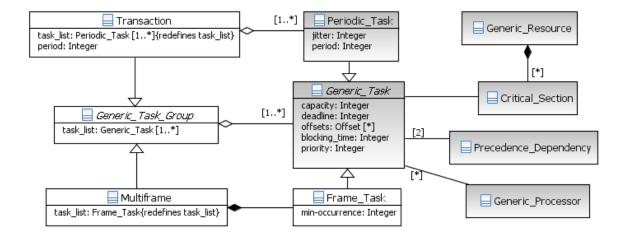

| Figure 5.7 C<br>Figure 5.8 T<br>Figure 5.9 T<br>Figure 5.10 M | Cheddar Framework Cheddar-ADL Partial Meta-Model: White boxes highlight extensions Cransaction with Two Tasks Crask Group Example Maximum Precedence Dependencies | 121<br>121<br>122 |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Figure 5.8 T<br>Figure 5.9 T<br>Figure 5.10 M                 | Transaction with Two Tasks                                                                                                                                        | 121<br>122        |

| Figure 5.9 T<br>Figure 5.10 M                                 | Task Group Example                                                                                                                                                | 122               |

| Figure 5.10 N                                                 |                                                                                                                                                                   |                   |

| _                                                             |                                                                                                                                                                   | 125               |

|                                                               | ransformation Duration by Number of Frames                                                                                                                        |                   |

| -                                                             | ransformation Duration by Number of Precedence Dependencies                                                                                                       |                   |

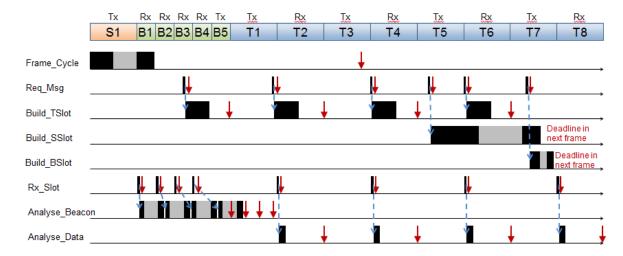

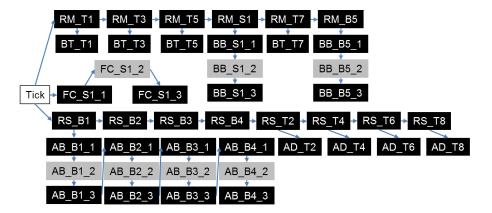

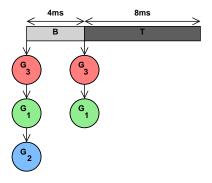

| •                                                             | DMA Frame and Threads of Real Case-Study                                                                                                                          |                   |

| _                                                             | ree-Shaped Transaction of Real Case-Study                                                                                                                         |                   |

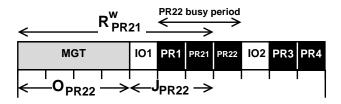

| 0                                                             | ree-Shaped Transaction with Non-Immediate Tasks                                                                                                                   |                   |

| 0                                                             | Inderestimation due to Non-Immediateness                                                                                                                          |                   |

| 0                                                             | Non-Immediateness and Jitter                                                                                                                                      | -                 |

|                                                               | Non-Immediateness and Interference                                                                                                                                |                   |

| -                                                             | nterference returned by $\tau_G$                                                                                                                                  |                   |

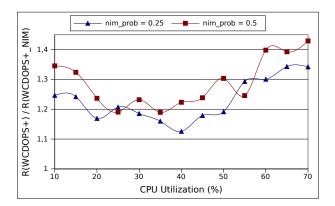

|                                                               | Comparison between WCDOPS+ and WCDOPS+NIM by Processor Utiliza-                                                                                                   | '                 |

| _                                                             | ion and Offset Increase Probability                                                                                                                               | 144               |

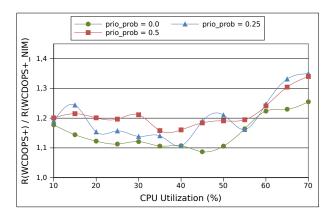

|                                                               | Comparison between WCDOPS+ and WCDOPS+NIM by Processor Utiliza-                                                                                                   |                   |

| _                                                             | ion and Random Priority Probability                                                                                                                               | 145               |

|                                                               | Partial Software Radio Protocol Case-Study                                                                                                                        |                   |

|                                                               | Thales Specification Document Figure                                                                                                                              |                   |

|                                                               | ervice Model Overview                                                                                                                                             |                   |

| -                                                             | ervice Behavior View Meta-Model                                                                                                                                   |                   |

|                                                               | ervice Behavior View Example                                                                                                                                      |                   |

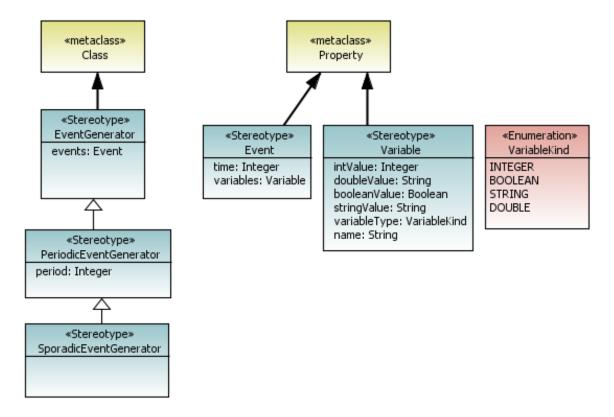

|                                                               | Event Generator Profile                                                                                                                                           |                   |

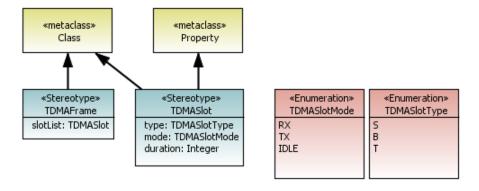

| _                                                             | DMA Profile                                                                                                                                                       |                   |

| -                                                             | Event Generator View Example                                                                                                                                      |                   |

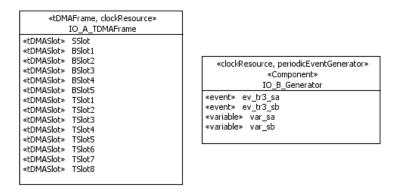

|                                                               | Thread Implementation View Meta-Model                                                                                                                             |                   |

| -                                                             | Thread Implementation View Example                                                                                                                                |                   |

|                                                               | ervice to Cheddar Overview                                                                                                                                        |                   |

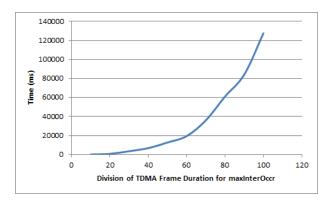

|                                                               | Transformation Time for TDMA Frame Durations                                                                                                                      |                   |

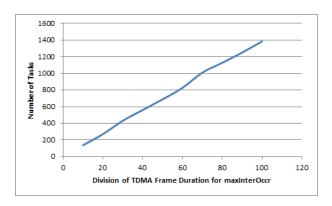

| -                                                             | Number of Cheddar-ADL Tasks for TDMA Frame Durations                                                                                                              |                   |

| Figure 7.13 T                                                 | Transformation Time Growth                                                                                                                                        | 163               |

| 0 -                                                           | Number of Tasks Growth                                                                                                                                            | _                 |

|                                                               | Original Cheddar-ADL Meta-Model                                                                                                                                   | 171               |

|                                                               |                                                                                                                                                                   |                   |

| Table 3.1 | Characteristics for Scheduling Analysis                                     | 77 |

|-----------|-----------------------------------------------------------------------------|----|

| Table 3.2 | Applicability of Task Models to Software Radio Protocol                     | 79 |

| Table 3.3 | Methods of Tests in Tools                                                   | 80 |

| Table 3.4 | Architecture Description Language Comparison                                | 85 |

| Table 4.1 | HDRN Task Parameters: Priorities in highest priority first order            | 92 |

| Table 4.2 | HDRN Shared Resources: Start and end times are those of critical sections . | 93 |

| Table 4.3 | High Level Software Architecture Model in UML MARTE                         | 94 |

| Table 4.4 | Execution Platform Model in UML MARTE                                       | 95 |

| Table 4.5 | Allocations                                                                 | 97 |

|           |                                                                             |    |

| Table 4.6                      | Computed WCRTs of HDRN Tasks                      | 98       |

|--------------------------------|---------------------------------------------------|----------|

| Table 4.7                      | Simulated WCRTs of HDRN Tasks                     | 01       |

| Table 5.1                      | DGMF Task Set                                     | 07       |

| Table 5.2                      | DGMF Example for GMF Test                         | 39       |

| Table 5.3                      | Transaction from DGMF Transformation              | 16       |

| Table 5.4                      | DGMF Generator Constraints and Assumptions        | 23       |

| Table 6.1                      | Transaction Generator Constraints and Assumptions |          |

| Table 6.2                      | Case-Study 1 Task Set                             |          |

| Table 6.3                      | Case-Study 1 WCRTs                                | 47       |

| Table 6.4                      | Task WCRTs of MAC Layer Case-Study                | 48       |

| Table 7.1                      | Service Behavior Mapping                          | -        |

| Table 7.2                      | Event Generator Mapping                           |          |

| Table 7.3                      | Thread Implementation Mapping                     |          |

| Table B.1                      | Task Parameters of Real Case-Study                |          |

| Table C.1                      | Service Analysis Entities                         |          |

| Table C.2                      | Service Analysis Mapping                          |          |

| Table C.3                      | Service Analysis Palette                          |          |

| Table C.4                      | Service Behavior Entities                         |          |

| Table C.5                      | Service Behavior Mapping                          |          |

| Table C.6                      | Service Behavior Palette                          | -        |

| Table C.7                      | Event Generator Entities                          | -        |

| Table C.8                      | Event Generator Mapping                           |          |

| Table C.9                      |                                                   | 80       |

| Table C.10                     |                                                   | 81       |

| Table C.11                     | Thread Implementation Mapping                     |          |

| Table C.12                     |                                                   | 82       |

| Table C.13                     | at 1                                              | 82       |

| Table C.14                     | Shared Resource Implementation Mapping            | 83       |

| Table C.15                     | Shared Resource Implementation Palette            |          |

| Table C.16                     | Operating System Implementation Entities          |          |

| Table C.17                     |                                                   | 85       |

| Table C.18                     | Operating System Implementation Palette           | _        |

| Table C.19                     | Hardware Implementation Entities                  | _        |

| Table C.20                     | Hardware Implementation Mapping                   | _        |

| Table C.21                     |                                                   | 86       |

| LIST O                         | F ALGORITHMS                                      | _        |

| Algorithm 2.1<br>Algorithm 2.2 |                                                   | 58       |

| Algorithm 2.3                  |                                                   | 59<br>61 |

| Algorithm 5.1                  | T. I. A. DOMER E. W.                              | 11       |

| Algorithm 5.2                  |                                                   | 14       |

| Algorithm 5.3                  | T                                                 | 14       |

| Algorithm 5.4                  | Transaction Release Time Modification             | •        |

| Algorithm 5.5                  | Reduce Precedence Dependencies                    | -        |

| Algorithm 6.1 | Immediate Function                        | 137 |

|---------------|-------------------------------------------|-----|

| Algorithm 6.2 | Modified TransactionInterference Function | 138 |

| Algorithm 6.3 | Modified BranchInterference Function      | 139 |

| Algorithm 6.4 | Modified TaskInterference Function        | 140 |

| Algorithm D.1 | Service to Cheddar                        | 187 |

| Algorithm D.2 | ReduceJobPrecs Procedure                  | 188 |

| Algorithm D.3 | ProcessNode Procedure                     | 189 |

| Algorithm D.4 | ProcessStep Function                      | 190 |

| Algorithm D.5 | ProcessThread Procedure                   | 190 |

| Algorithm D.6 | ProcessScheduler Function                 | 191 |

| Algorithm D.7 | ProcessPartition Function                 | 191 |

| Algorithm D.8 | ProcessResAcq Procedure                   | 192 |

| Algorithm D.9 | ProcessSharedResource Function            | 192 |

|               |                                           |     |

# **ACRONYMS**

AADL Architecture Analysis & Description Language

ADL Architecture Description Language

ASIC Application-Specific Integrated Circuit

AUTOSAR AUTomotive Open System ARchitecture

**BCET Best Case Execution Time**

**BCRT** Best Case Response Time

CAN Controller Area Network

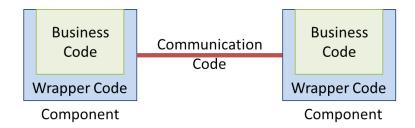

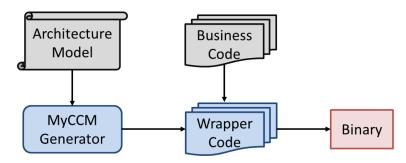

свм Component-Based Model

ссм CORBA Component Model

CORBA Common Object Request Broker Architecture

DAG Directed Acyclic Graph

**DGMF** Dependent General Multiframe

Dм Deadline-Monotonic

DP Dynamic Priority

DPCP Dynamic Priority Ceiling Protocol

DRT Digraph Real-time Task

**DSP** Digital Signal Processor

DVFS Dynamic Voltage and Frequency Scaling

**EDF** Earliest Deadline First

**EMF** Eclipse Modeling Framework

**FP** Fixed Priority

FPGA Field-Programmable Gate Array

FPS Frames Per Second

GCM Generic Component Model

GMF General Multiframe

GPP General Purpose Processor

GQAM General Quantitative Analysis Model

GRM General Resource Model

HDRN Highly Dynamic Radio Network

ньам High Level Application Model

ням Hardware Resource Model

**IP Internet Packet**

IPCs Internet Packet Convergence Sub-layer

**IT Information Technology**

LLF Least Laxity First

MAC Media Access Controller

MANET Mobile ad-hoc wireless NETwork

MARTE Modeling and Analysis of Real-Time Embedded systems

MDE Model-Driven Engineering

муссм Make your CORBA Component Model

ом GObject Management Group

os Operating System

osi Open Systems Interconnection

**PAM** Performance Analysis Model

PCP Priority Ceiling Protocol

рну PHYsical

PIP Priority Inheritance Protocol

POSIX Portable Operating System Interface

gos Quality of Service

RLC Radio Link Control

RM Rate-Monotonic

**RRT Recurring Real-time Task**

RSA Rational Software Architect

RSN Radio Sub-Network

RTA Response Time Analysis

RTES Real-Time Embedded System

s2c Service to Cheddar

SAM Scheduling Analysis Model

srm Software Resource Model

SRP Stack Resource Policy

TDMA Time Division Multiple Access

**UML** Unified Modeling Language

**VSL** Value Specification Language

wсвт Worst Case Blocking Time

WCET Worst Case Execution Time

WCRT Worst Case Response Time

хмь Exensible Markup Language

# **PUBLICATIONS**

Some ideas and figures of this thesis have appeared previously in the following publications. In the conclusion of each chapter of this thesis, it will be reminded which publications contain the contributions of the chapter.

#### **BOOK CHAPTER**

[26] M. Bourdellès, S. Li, I. Quadri, E. Brosse, E. Gaudin, F. Mallet, A. Goknil, A. Sadovykh, D. George, and J. Kreku, "Fostering analysis from industrial embedded systems modeling," in *Industry and Research Perspectives on Embedded System Design*, IGI Global, 2014.

#### **JOURNAL**

[82] S. Li, F. Singhoff, S. Rubini, and M. Bourdellès, "Applicability of real-time schedulability analysis on a software radio protocol," *ACM SIGAda Ada Letters*, vol. 32, no. 3, pp. 81-94, Dec. 2012.

#### CONFERENCE

- [84] S. Li, F. Singhoff, S. Rubini, and M. Bourdellès, "Scheduling Analysis of TDMA-Constrained Tasks: Illustration with Software Radio Protocols," in *Proceedings of the 11th IEEE International Conference on Embedded Software and Systems (ICESS'14)*, Paris, France, 2014. (Acceptance rate = 24.7%; Best paper award)

- [83] S. Li, F. Singhoff, S. Rubini, and M. Bourdellès, "Extending Schedulability Tests of Tree-Shaped Transactions for TDMA Radio Protocols," in *Proceedings of the 19th IEEE International Conference on Emerging Technology & Factory Automation (ETFA'14)*, Barcelona, Spain, 2014.

- [81] S. Li, S. Rubini, F. Singhoff, and M. Bourdellès, "A Task Model for TDMA Communications," in *Proceedings of the 9th IEEE International Symposium on Industrial Embedded Systems Work in Progress (SIES'14)*, Pisa, Italy, 2014.

#### WORKSHOP

- [80] S. Li, S. Rubini, F. Singhoff, and M. Bourdellès, "Applying Holistic Schedulability Tests to Industrial Systems: Experience and Lessons Learned," in *Proceedings of the 5th International Workshop on Analysis Tools and Methodologies for Embedded and Real-time Systems (WATERS'14)*, Madrid, Spain, 2014.

- [27] M. Bourdellès and S. Li, "PRESTO project, automatic code instrumentation from (Modelio based) models to process performance analysis at the software integration phase," presented at *FITTEST'12*, Paris, France, 2013.

- [78] S. Li, M. Bourdellès, A. Acebedo, J. Botella, and F. Peureux, "Experiment on Using Model-Based Testing for Automatic Tests Generation on a Software Radio Protocol," in *Proceedings of the 9th International Workshop on Systems Testing and Validation (STV'12)*, Paris, France, 2012.

- [77] S. Li, "PRESTO: Results from execution trace analysis," in *Joint Proceedings of Co-located Events at the 8th European Conference on Modelling Foundations and Applications (ECMFA'12)*, Copenhagen, Denmark, 2012.

- [113] I. Quadri and S. Li, "PRESTO: Improvements of Industrial Real-time Embedded Systems Design and Development," in *OMG Workshop on Real-Time*, Embedded and Entreprise-Scale Time-Critical Systems, Paris, France, 2012.

# INTRODUCTION

#### CONTEXT

Real-Time Embedded Systems (RTES) [74] are part of our daily life today. Their usage ranges from specific industrial equipment, like factory robots, to general civilian devices, like smartphones and tablets. A RTES is both an embedded and a real-time system.

An embedded system is a computing system composed of hardware and software, with a specific mission to accomplish, using limited resources. Examples of resources are energy and processors. Embedded systems may interact with the environment in which they execute. The environment may be the physical components of a vehicle to the electromagnetic waves that surround us. The environment in which the embedded system executes, evolves within time. As such, an embedded system is usually subject to real-time computing.

A real-time system is a computing system composed of hardware and software, where computing is subject to time constraints. Therefore the correctness of a real-time system's computing is not only judged by the correctness of the produced data, i.e. functional correctness, but also the time at which the data is produced, i.e. temporal correctness.

Nowadays the software of a RTES is usually multi-tasked. It is composed of several tasks that are units of execution, sharing concurrently the limited processors. The system may be uniprocessor or multiprocessor.

Since the tasks are part of a real-time system, they have time constraints, expressed as deadlines. Once a task is released, we say a job of the task is released, and the job has to complete execution before some deadline.

A task does not execute alone, and several tasks share processors. Scheduling [85] is the method that decides which task has access to the processors during execution and we say that the tasks are scheduled on the processors by a scheduling policy.

Scheduling decisions are taken by considering the priority of a task, which indicates its importance. Priorities may be static or dynamically updated during execution. For multiprocessor systems, scheduling also determines whether tasks may or may not execute on any processor. When tasks can execute on any processor, the scheduling is global. When a task is allocated on a processor and can only execute on that processor, the scheduling is partitioned.

Scheduling analysis [126] is the method used to verify that tasks will meet their deadline, when they are scheduled on the processors. Scheduling analysis can potentially be complex due to the interactions between the tasks. These interactions come in the form of synchronization through software shared resources, which are software entities accessed mutual-exclusively by tasks. The interactions may also come in the form of precedence dependency between tasks, which means the release of a task depends on the completion of a preceding task. Precedence dependencies may be due to communications between tasks.

Some methods, part of scheduling analysis, are schedulability tests. Such tests assesses if all jobs of all tasks will meet their deadlines during execution, when the tasks are scheduled on processors by a specific scheduling policy. Schedulability tests may compute the response time of tasks. The response time is the time between the release of the task and its completion. The response times are compared to deadlines to assess schedulability.

Schedulability tests are associated with task models that abstract the architecture of a RTES for the analysis. There are several task models in the literature that consider more or less interactions between tasks, and characteristics of the execution environment that hosts the tasks. Scheduling analysis is necessary for the development of some Real-Time Embedded System (RTES). For example, certain radio equipments are typical RTES. This kind of system receives radio electromagnetic waves, maintains a link with other radio stations in the network, and communicates with them. When radio stations communicate, some radio protocol needs to be defined and implemented. Radio protocols may be impacted by the method to access the shared communication medium between several radio stations.

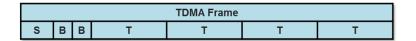

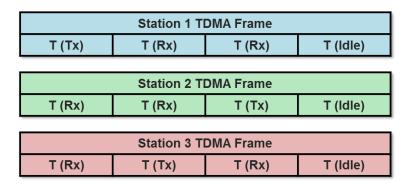

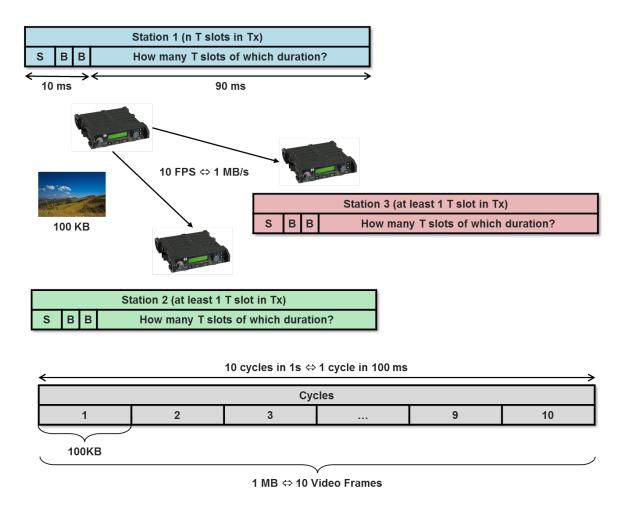

One common method, implemented by radio protocols to access the shared medium, is Time Division Multiple Access (TDMA) [30]. In TDMA, time is divided into several time slots and at each time slot, a radio either transmits its data, or receives some data. TDMA is one reason, among others, that some activities of a radio protocol are divided into time slots. Therefore there are time constraints in systems that use the TDMA method.

Traditionally radios were implemented as dedicated hardware components. Trends in the last two decades have seen the emergence of software radios [99], where more and more components are implemented as software. This is the case for the radio protocol, which is then called a software radio protocol.

In software radio protocols, activities are implemented by software tasks, that are time-constrained. The time constraints must be considered in the development of such a system. Thus scheduling analysis needs to be applied, during the development of a software radio protocol.

Software radios are one of the main products developed at Thales Communications & Security (TCS). There is a will at TCS to integrate scheduling analysis in the development cycle of its products, especially for software radio protocols.

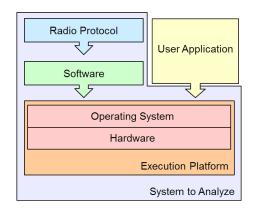

During the development cycle, the system architecture is modeled and the architecture models are exploited either for code generation, or for documentation. Models are made using languages such as Make your CORBA Component Model (MyCCM) [25]. MyCCM is a component-based model developed at Thales. It is dedicated to code generation. Thales also participates in the standardization Modeling and Analysis of Real-Time Embedded systems (MARTE) [42], a profile for the Unified Modeling Language (UML) that extends it for the design and analysis of RTES.

This thesis is on scheduling analysis of software radio protocols. It has been done in collaboration between Thales Communications & Security and the Université de Bretagne Occidentale.

#### OBJECTIVE AND PROBLEMS

The objective of this thesis is to analyze the schedulability of a software radio protocol that uses TDMA. The analysis method must be automatic, to be integrated into the development cycle.

As we will see, current task models and schedulability tests are not applicable to a software radio protocol that uses a time-division multiplexing method to access the shared medium. Therefore a task model and a schedulability test must be proposed for such a system, and they must be adapted for the characteristics of the system.

In order to automate the analysis, there are two issues to solve. We will see that task models are complex to be used directly by engineers. Task models and their analysis methods must thus be implemented in a tool. But currently not all task models and their analysis methods are implemented in available tools.

Another issue to solve, in order to automate the analysis, is the applicability of an Architecture Description Language (ADL) for scheduling analysis. Indeed, the tasks set for the analysis must be produced automatically from architecture models described with an ADL, used by engineers. We will see that scheduling analysis has not been performed automatically with an ADL specific to the software radio protocol domain.

#### OVERVIEW OF THE SOLUTION

To solve the issue of task models, a new task model and its analysis method are proposed in this thesis. This work is based on characteristics of real software radio protocols developed at Thales. The task model is an extension of an existing one in the literature. The choice of the task model to extend is made by experiments. The new task model is applicable to the characteristics of a software radio protocol.

In the work of this thesis, the proposed task model and its analysis method are implemented in Cheddar, an open-source scheduling analysis tool. We will see how the tool is extended.

A model conforming to the task model is then produced automatically from an architecture model of the system. Since scheduling analysis has not been performed with an ADL specific to the software radio protocol domain, this thesis proposes to experiment with UML MARTE, a generic modeling language for the RTES domain. MARTE is chosen because there exists a transformation of its architecture models to development models used by engineers at Thales Communications & Security.

#### CONTRIBUTIONS

The solution proposed in this thesis is the result of works that propose several contributions.

#### Extension of the General Multiframe Task Model

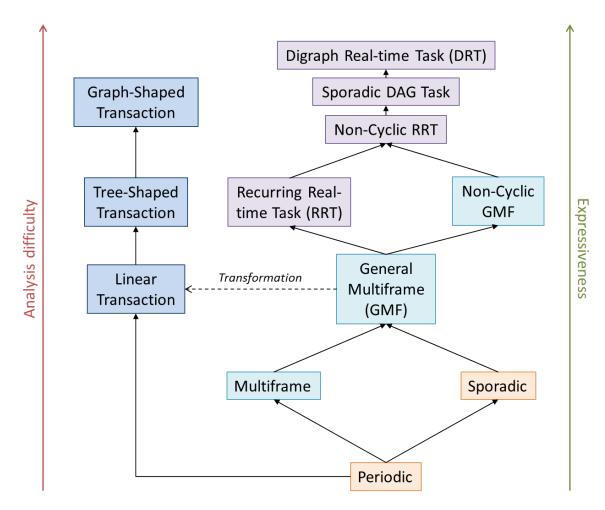

This thesis proposes the Dependent General Multiframe (DGMF) task model, an extension of the General Multiframe (GMF) task model [14]. A GMF task is a vector of frames that represent the jobs of the task. The jobs may not have the same parameters, such as deadline and execution time. It is thus possible in the GMF task model to represent individual job parameters of a task.

On the other hand, precedence dependencies and shared resources cannot be modeled in GMF, and thus they are not considered by the schedulability tests for GMF. Furthermore, GMF is applicable to a uniprocessor systems.

The DGMF task model extends GMF with precedence dependencies and shared resources. The DGMF task model is also applicable to a multiprocessor system with partitioned scheduling.

GMF was not originally proposed for a specific domain. This task model was motivated by generic multimedia and control-command systems. Thus DGMF can also be applied to other domains than software radio protocols, for example the mentioned ones.

#### DGMF to Transaction

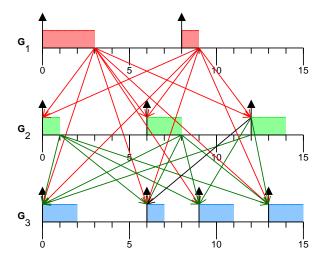

The analysis method for DGMF consists in exploiting another kind of model called transaction [143]. A transaction is a group of tasks related by precedence dependency. This thesis proposes an algorithm to transform DGMF tasks to transactions. The transformation solves the issue of difference in semantic between the two models.

#### Extension of Schedulability Test for Transactions

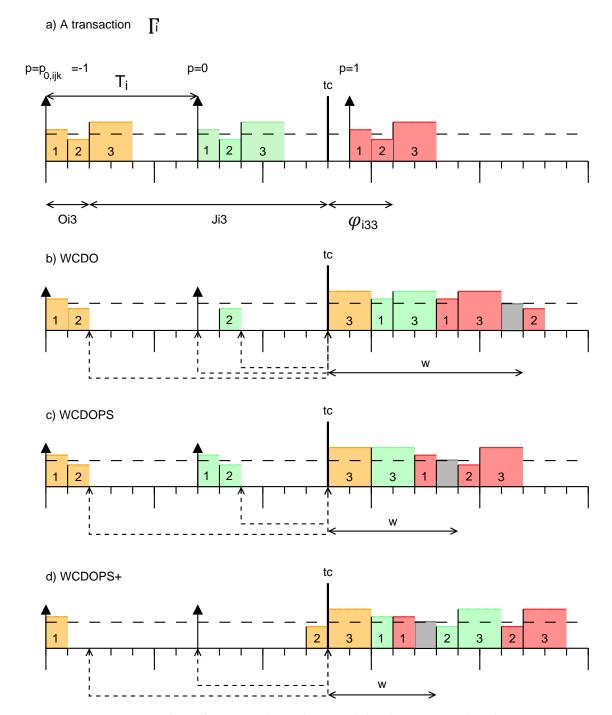

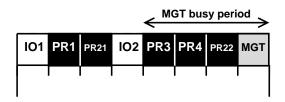

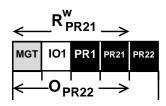

The transactions that are the results of the transformation have some characteristics not considered by current schedulability tests for transactions. Thus this thesis proposes the WCDSOP+NIM test, which is an extension of the WCDOPS+ test in [118]. The extension considers non-immediate tasks, which have a specific kind of task release.

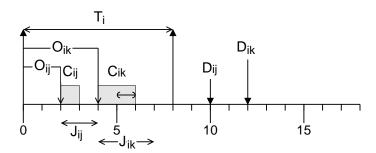

Consider a successor task that has a precedence dependency with its predecessor task. In the immediate case, the predecessor task releases immediately the successor task, upon completion. In the non-immediate case the predecessor does not necessarily release immediately the successor task. For example, if the predecessor completes before the earliest release time of the successor task, the successor task is not released immediately.

This kind of release must be considered by the schedulability test. Otherwise, as we will see, the response times computed by the test may be overestimated or underestimated. These problems are solved by the schedulability test proposed in this thesis.

Transactions are not domain-specific and thus the schedulability test proposed in this thesis can be applied to other domains than software radio protocols.

#### Automatic Analysis with UML MARTE Models

To exploit the transaction and DGMF task models, an architectural model is proposed in UML MARTE. MARTE lacks clearly defined semantics for a specific RTES domain, and modeling guidelines.

This thesis thus shows an experience on modeling a software radio protocol with the UML MARTE modeling language. The model is described with UML structural diagrams and activity diagrams. The model is transformed automatically to the task model proposed in this thesis, for scheduling analysis.

Although initially motivated by software radio protocols, the model uses concepts of UML MARTE, which is a generic modeling language for RTES domains.

#### Available Tools

The GMF, DGMF, transaction models, and their analysis methods, are all implemented in Cheddar. As a reminder, Cheddar is an open-source scheduling analysis tool, available for both the research and industrial communities.

The UML MARTE model was done in Papyrus, an open-source modeler of Eclipse. The transformation of the UML MARTE model is implemented as a generic plug-in for Eclipse. The plug-in works on any model respecting the Eclipse implementation of UML.

#### THESIS ORGANIZATION

This thesis is divided into six chapters that are organized as follows.

In Chapter 1, a detailed presentation of RTES is given. This chapter focuses on entities of such a system concerned by scheduling. Some basic scheduling policies are presented. The chapter also exposes some development methods for RTES, focusing on models.

Chapter 2 gives a perspective of scheduling analysis. Some fundamental task models are presented and their analysis methods are explained. The chapter shows the relation of generalization between the different task models. The expressiveness of a task model, compared to its analysis difficulty, is discussed.

In Chapter 3, the software radio protocol system is presented. This chapter defines the assumptions and context of the work. It gives some details on the problems faced when trying to apply scheduling analysis to such a system. An overview of the solution is then presented.

Since no task models are applicable, the idea is to extend an existing one from the literature. To decide which task model to extend, an experiment is done in Chapter 4. This experiment consists in applying a fundamental task model to a software radio protocol. The task model is applied by modeling the system in UML MARTE, and transforming it to the task model.

The DGMF task model, extension of GMF, is proposed in Chapter 5. We will see how DGMF can be transformed into transactions and how tests for transactions need to be adapted for specific needs of DGMF tasks.

In Chapter 6, the WCDOPS+NIM schedulability test is presented. The schedulability test is applicable to tree-shaped transactions with non-immediate tasks. The chapter exposes the consequences of non-immediateness, before presenting the algorithm of the test.

DGMF tasks and transactions should be automatically produced from a system architecture model. For this purpose, in Chapter 7, the UML MARTE model of Chapter 4 is extended. The extension is based on existing Thales specification documents. The transformation of the UML MARTE model is then presented.

This thesis concludes by exposing some technical and methodological future works. The appendix sections contain technical details that will be referenced throughout the chapters.

# Part I STATE OF THE ART

# Chapter 1

# REAL-TIME EMBEDDED SYSTEM

Systems called Real-Time Embedded System (RTES) are now part of our daily life today. Their usage ranges from flight navigation software for avionic systems, to sensor data processing in autonomous vehicles, to everyday communication systems in smartphones. Unlike an Information Technology (IT) system, a RTES has special characteristics.

In this chapter, the concept of RTES is first defined. Then some of the entities of its architecture are presented: software, operating system, and hardware. Afterwards let us focus on the development cycle of a RTES. A development method called model-drive engineering, and its concepts, are presented. The application of this method and its concepts to RTES is the main focus.

#### 1.1 GENERALITIES ON REAL-TIME EMBEDDED SYSTEMS

A RTES is both an embedded system and a real-time system. This sections defines such systems and describes their characteristics.

**Definition 1** (Embedded System [74]). An embedded system is a computing system composed of hardware and software, with a specific mission to accomplish, using limited resources (e.g. processing, memory, battery). This kind of system is embedded within a larger system. The embedded system, or the system that hosts it, may have an interaction with the environment in which it executes.

As embedded systems may interact with their environment, for which the state evolves in time, they are also often real-time systems.

**Definition 2** (Real-time System [135, 32, 74]). A real-time system is a computing system composed of hardware and software, where computing is subject to time constraints. A real-time system takes as input some data then launches some behavior, or produces some data as output, within a time limit. As such the correctness of a real-time system's computing is not only judged by the correctness of the produced data (functional correctness), but also the time at which the data is produced (temporal correctness). Time constraints are generally referred as deadlines.

A RTES can be characterized by its time constraints:

- Hard Real-Time: In hard real-time systems, time constraints must be met at all cost. The violation of time constraints may lead to human or material damage [150]. Examples of hard real-time systems are flight controls, nuclear plant control systems.

- Soft Real-Time: In soft real-time systems, time constraints must be met but their violation can be tolerated [72], sometimes only leading to a decreased Quality of Service (QoS) without any damage on the environment with which the system interacts. Examples of soft real-time systems are video decoders.

- Mixed-Criticality: Mixed-criticality systems [13] have constraints that must be met and constraints for which the violation is tolerable. In terms of time constraints, this means that some time constraints may be missed, but there is a limit to the number of times a time constraint is not respected. An example of a mixed-criticality system is a flight information system that

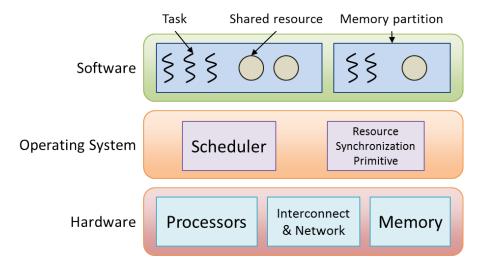

Figure 1.1: RTES Architecture

coexists with a flight control system. The flight control system has a higher criticality than the flight information system.

A RTES can also be characterized by the entities of its architecture. Figure 1.1 shows a very simplified architecture of a RTES. The *software* layer contains some tasks and shared resources in memory partitions. The *operating system* layer contains a component called scheduler, that schedules the tasks of the software. It also contains some primitives to protect the shared resources. Finally the *hardware* layer has some hardware components, like processor, bus and memory. The execution of the software and operating system is supported by these hardware components.

In the following three sections, the three layers of Figure 1.1 are described in detail and their entities are defined.

#### 1.2 SOFTWARE OF A RTES

The software of a RTES accomplishes the mission of the system, with the help of the Operating System (OS) and hardware. It takes as input some data and, executes some operations, and may produce some data as output. These systems are sometimes called control-command systems. The operations must be done within some time constraint which must be met.

There are several ways to design the software of a RTES. Among these designs let us focus on the multi-tasking approach. In the following sections, the task concept is first defined. Then some types of tasks are presented. Afterwards common parameters of a task are defined. Tasks may have dependencies, through precedence and shared resource. These dependencies will be defined. Finally tasks are allocated in a memory partition, which are presented of the last section.

#### 1.2.1 Concept of Task

In the multi-tasking design, the software has several units of execution, called tasks. In this section the concept of a task is defined and then its life cycle is exposed.

**Definition 3** (Task [3, 126]). A task is a unit of execution in a software. Each time a task is released, we say that a job of the task is released. Once released, a task has a number of instructions to execute sequentially. Instructions are executed on a processor and are either for computing or synchronization with other tasks.

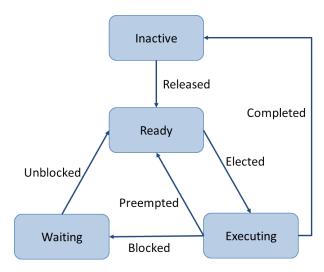

A task has a life cycle composed of several states. Figure 1.2 shows these states:

Figure 1.2: Task Life Cycle

- Inactive: Once the task is created, it starts in the inactive state. It does not have any data to handle, nor any operation to execute. When an event occurs, indicating to the task that it must handle some data and execute some operations, it is released and goes to the ready state.

- Ready: In the ready state, the task is waiting to be elected, among other tasks, for execution.

The election process will be explained in later sections that describe the OS of a RTES.

- Executing: Once elected, the task executes its instructions on a processor. During execution, if at some point an instruction asks for some unavailable resource, the task goes to the waiting state. Furthermore if a task is executing on a processor, and another task is elected to execute on the same processor, then the executing task is interrupted and goes back to the ready state. It then waits to be elected again to resume it left off its execution. This phenomenon is called preemption. Finally once a task completes execution, it goes back to the inactive state.

- Waiting: When a task is waiting for a resource to become available, it is in this state. We say that the task is blocked. Once the resource becomes available, the task goes to the ready state to be elected for execution.

#### 1.2.2 Types of Task

Tasks may be released by events occurring by different patterns. The release pattern can be used to define the type of the task:

- Periodic task [85]: Once a periodic task is released a first time, its next jobs are released in strictly regular intervals called the period. The periodic release mechanism may be implemented as a timer for example. An example of a periodic task is one that polls data from a sensor regularly.

- Sporadic task [16]: A sporadic task is released regularly, without necessarily a strict period. On the other hand the minimum time between two releases is known. A periodic task is a particular case of a sporadic task. An example of a sporadic task is one released by incoming Internet Packet (IP) packets. The IP packets arrive more or less quickly but the rate of arrival cannot be higher than the throughput of the network infrastructure.

- Aperiodic task [133, 137]: An aperiodic task is a task for which the minimum time between two releases is unknown, nor the first release time.

Tasks are said synchronous or asynchronous depending on when the tasks are released for the first time.

**Definition 4** (Synchronous [5]). Tasks are said synchronous if the first jobs of the tasks are released at the same time.

**Definition 5** (Asynchronous [17, 108]). Tasks are said asynchronous if there is at least one first job of a task that is not released at the same time as the other first jobs of other tasks.

#### 1.2.3 Parameters of Task

Let us now see some parameters of a task that describe it. In the previous section, we saw how a task is released. Task releases may be subject to some jitter.

**Definition 6** (Jitter [143, 105]). A task released at earliest at t, and experiencing a release jitter of J, is released at any time in [t; t+J].

Jitter may be due to coarse grain clocks in the system. For example a task may have a period of 1  $\mu s$  but the system clock is only as accurate as every 5  $\mu s$ . Another example of jitter is when the scheduler in the OS switches from one executing task to another that just got elected. This phenomenon is called context switch.

Since tasks are in concurrence for access to the processor, there must be some mechanism to determine which task is of higher priority than another, for access to the processor, at any given time.

**Definition 7** (Priority [3, 126]). A task's priority indicates its order of importance for scheduling.

We say that a task is of higher priority than another. At a given time, the highest priority task in the ready state should have access to the processor for execution.

The number of instructions executed by a task may be described by its execution time.

**Definition 8** (Execution Time [10]). *The processor time taken by a task to execute its instructions is called an execution time.*

A task may not always execute the same set of instructions from a job to another. This means its execution time can vary from one job to another. The upper and lower bounds of its execution time are called Worst Case Execution Time (WCET) and Best Case Execution Time (BCET).

**Definition 9** (Worst Case Execution Time [149]). The WCET of a task is the longest execution time of a task

**Definition 10** (Best Case Execution Time [149]). The BCET of a task is the shortest execution time of a task.

The execution time does not describe the total time taken by a task to complete its instructions. This time value is described by the response time of a task.

**Definition 11** (Response Time [105]). *The time from a task's release to its completion is called a response time.*