Université de Bretagne Occidentale UFR Sciences et Techniques

# Étude et qualification amont d'un contrôleur domotique contraint par le temps à l'aide du langage d'architecture AADL

#### Mathieu Soula

Mémoire de 2<sup>e</sup> année de Master Recherche Spécialité Logiciels pour les systèmes embarqués Année universitaire 2013-2014

Tuteur : Frank Singhoff Encadrant : Loïc Plassart

| "The computing scientist's main challenge is not to get confused by the complexities of his own making."                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Edsger Wybe Dijkstra<br>Mathématicien et informaticien Néerlandais, prix Turing 1972                                                                           |

|                                                                                                                                                                |

| "Software and cathedrals are much the same – first we build them, then we pray."                                                                               |

| Samuel T. Redwine<br>Professeur à l'université James Madison, Harrisonburg                                                                                     |

|                                                                                                                                                                |

| "Weinberg's Second Law: If builders built buildings the way programmers wrote programs, then the first woodpecker that came along would destroy civilization." |

Informaticien et professeur de psychologie et d'anthropologie du développement logiciel Auteur de *The Psychology of Computer Programming and Introduction to General*

Gerald Marvin Weinberg

Systems Thinking

#### Remerciements

Je tiens à remercier toutes les personnes qui ont rendu ce stage possible par leur aide et leurs contributions.

Je souhaite tout d'abord remercier mon responsable de formation Jalil BOUKHOBZA pour avoir accepté mon inscription en deuxième année de master Logiciels pour les Systèmes Embarqués.

Je remercie également Frank SINGHOFF, professeur à l'Université de Bretagne Occidentale, pour son soutien et pour l'aide qu'il a apportée tout au long de ce stage. Ses conseils ont été utiles afin de mener à bien ce projet.

Enfin, je remercie Loïc Plassart, président de l'association Tréflévenet, pour avoir suivi mes travaux durant ce stage. Son expérience et ses conseils avisés ont rendu possible la réalisation du travail présenté dans ce rapport.

#### Table des matières

| 11101 | ntroduction                                  |                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cor   | ntexte                                       | de la description d'architecture logicielle                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.1   | Notion                                       | ns des langages de description d'architecture                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | 2.1.1                                        | Définition de la description d'architecture                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | 2.1.2                                        | Définition de langage de description d'architecture                                                                                                             | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|       | 2.1.3                                        | Composition d'un langage de description d'architecture                                                                                                          | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2.2   | Préser                                       | ntation de AADL                                                                                                                                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 2.2.1                                        | Eléments du langage                                                                                                                                             | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 2.2.2                                        | Extension du langage                                                                                                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 2.2.3                                        | Quelques outils                                                                                                                                                 | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.3   | Théor                                        | ie d'ordonnancement temps-réel                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 2.3.1                                        | Modèle canonique d'une tâche                                                                                                                                    | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 2.3.2                                        | Méthodes de vérification de l'ordonnançabilité d'un système                                                                                                     | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.4   | Descri                                       | ption d'architecture et qualification temps-réel                                                                                                                | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.5   | Concl                                        | usion                                                                                                                                                           | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Mo    | délisat                                      | ion du contrôleur domotique avec AADL                                                                                                                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.1   | Descri                                       | ption du système domotique                                                                                                                                      | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 3.1.1                                        | Réseau domotique considéré                                                                                                                                      | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 3.1.2                                        | Exigences fonctionnelles                                                                                                                                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 3.1.3                                        | Exigences non fonctionnelles                                                                                                                                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.2   | Préser                                       | ntation du modèle de contrôleur domotique                                                                                                                       | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

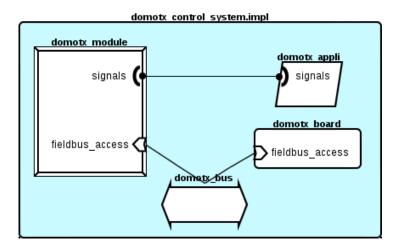

|       | 3.2.1                                        | Modélisation du réseau domotique                                                                                                                                | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 3.2.2                                        | Modélisation du contrôleur central                                                                                                                              | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>Mo<br>3.1 | 2.1 Notion 2.1.1 2.1.2 2.1.3 2.2 Préser 2.2.1 2.2.2 2.2.3 2.3 Théor 2.3.1 2.3.2 2.4 Descri 2.5 Conclus  Modélisat 3.1 Descri 3.1.1 3.1.2 3.1.3 3.2 Préser 3.2.1 | Contexte de la description d'architecture logicielle  2.1 Notions des langages de description d'architecture  2.1.1 Définition de la description d'architecture  2.1.2 Définition de langage de description d'architecture  2.1.3 Composition d'un langage de description d'architecture  2.1.4 Définition de langage de description d'architecture  2.2 Présentation de AADL  2.2.1 Eléments du langage  2.2.2 Extension du langage  2.2.3 Quelques outils  2.3 Théorie d'ordonnancement temps-réel  2.3.1 Modèle canonique d'une tâche  2.3.2 Méthodes de vérification de l'ordonnançabilité d'un système  2.4 Description d'architecture et qualification temps-réel  2.5 Conclusion  Modélisation du contrôleur domotique avec AADL  3.1 Description du système domotique  3.1.1 Réseau domotique considéré  3.1.2 Exigences fonctionnelles  3.1.3 Exigences non fonctionnelles  3.2 Présentation du modèle de contrôleur domotique  3.2.1 Modélisation du réseau domotique  3.2.1 Modélisation du réseau domotique |

2 Table des matières

|    | 3.3                                                      | Conclu  | asion                                                  | 31 |

|----|----------------------------------------------------------|---------|--------------------------------------------------------|----|

| 4  | Ana                                                      | alyse d | e performances temps-réel avec AADL                    | 33 |

|    | 4.1                                                      | Métho   | dologie globale                                        | 33 |

|    | 4.2                                                      | Estima  | ation des caractéristiques du jeu de tâches            | 34 |

|    |                                                          | 4.2.1   | Détermination des capacités des tâches                 | 34 |

|    |                                                          | 4.2.2   | Caractérisation du jeu de tâches                       | 36 |

|    | 4.3                                                      | Implai  | ntation du modèle du contrôleur                        | 38 |

|    |                                                          | 4.3.1   | Implantation du processeur de la carte électronique    | 38 |

|    |                                                          | 4.3.2   | Implantation des threads du processus du contrôleur    | 39 |

|    |                                                          | 4.3.3   | Accès exclusif au bus de terrain                       | 40 |

|    |                                                          | 4.3.4   | Modification du modèle pour compatibilité avec Cheddar | 40 |

|    | 4.4                                                      | Analys  | se des résultats                                       | 41 |

|    |                                                          | 4.4.1   | Déroulement des tests de faisabilité                   | 41 |

|    |                                                          | 4.4.2   | Déroulement des simulations d'ordonnancement           | 42 |

|    | 4.5                                                      | Conclu  | ısion                                                  | 43 |

| 5  | Con                                                      | clusio  | n générale                                             | 45 |

| A  | Mo                                                       | délisat | ion haut-niveau du contrôleur central en AADL          | 47 |

| В  | B Modélisation complète du contrôleur central en AADL 51 |         |                                                        |    |

| Ré | éfére                                                    | nces b  | ibliographiques                                        | 57 |

Introduction

Un système embarqué est un système électronique et informatique autonome dédié à une tâche particulière et contenu dans un système englobant. Dans ce type d'environnement, le logiciel est fortement couplé au matériel, c'est pourquoi on parle de logiciel embarqué. Le domaine d'action d'un tel type de logiciel est toujours limité aux fonctions pour lesquelles il a été créé.

On assiste depuis quelques années à une explosion du nombre de systèmes embarqués destinés à un public non professionnel. Ceci est notamment visible dans le secteur de la téléphonie et de la domotique où les constructeurs cherchent constamment à créer de nouveaux équipements proposant des fonctionnalités novatrices. Les systèmes devenant de plus en plus complexes, leur coût de production tend à augmenter sensiblement. De nouvelles méthodes de conception ont donc été pensées afin de réduire ces coûts. Les frameworks de description d'architecture proposent par exemple une notation formelle permettant de décrire un système logiciel en tenant à la fois compte de l'aspect logiciel et de l'aspect matériel. Grâce à des outils d'analyses et de vérifications, ces solutions permettent de déplacer une partie du travail de qualification en amont des phases de conception.

Loïc Plassart de l'association TréflévéNet [Tréflévénet, 2014], travaille à la conception d'un contrôleur domotique. Ce contrôleur devra assurer plusieurs fonctions (affichage d'une interface graphique, commande de chauffage, commande d'éclairage, pilotage d'entrées-sorties, gestion d'un bus de terrain, etc.). Il souhaite désormais pouvoir qualifier son système pour s'assurer du bon respect des exigences fonctionnelles et non fonctionnelles. Cette qualification a la particularité d'être réalisée avant l'étape de conception du contrôleur.

L'objectif de mon stage consiste à réaliser une étude qualificative du contrôleur domotique. Concrètement, mon travail consistera tout d'abord à proposer un modèle d'architecture du contrôleur. Pour cela, le langage de description d'architecture AADL sera utilisé. Dans un second temps, je devrai réaliser un ensemble de tests afin de vérifier si le modèle défini répond ou non aux différentes exigences temporelles du système. J'utiliserai pour cela le moteur de Cheddar v3, un outil d'analyse de performances développé à l'Université de Bretagne Occidentale et qui peut être utilisé sur des modèles d'architecture écrits avec le langage AADL.

4 Introduction

Le mémoire est structuré de la manière suivante. Le chapitre 2 présente un état de l'art sur les langages de description d'architecture logicielle, introduit le langage AADL, et rappelle quelques bases sur la théorie d'ordonnancement temps-réel. Le chapitre 3 décrit le travail de modélisation du contrôleur domotique. Puis, le chapitre 4 présente les tests d'ordonnançabilité réalisés sur ce modèle. Enfin, le mémoire se conclut au chapitre 5 dans lequel sont présentées les perpectives d'évolutions possibles de mon travail.

2

## Contexte de la description d'architecture logicielle

Ce chapitre a pour but de délimiter les différents domaines concernés par ce stage. Il s'agit ici de constituer un état de l'art de la description d'architecture, plus particulièrement dans le domaine des logiciels. Dans une première partie, nous présentons un ensemble de définitions afin de mieux appréhender le domaine des langages de description d'architecture. Puis dans une seconde partie, nous proposons une introduction au langage de description d'architecture AADL. Puis dans une troisième partie, nous donnons quelques notions de la théorie d'ordonnancement temps-réel qui seront utiles à la lecture de ce rapport. Enfin, nous terminons ce chapitre en discutant de quelques travaux de modélisation AADL dans une optique de qualification temporelle de systèmes.

Dans le reste de ce document, nous utiliserons l'acronyme **AD** pour faire référence au terme description d'architecture, et l'acronyme **ADL** pour faire référence au terme langage de description d'architecture.

#### 2.1 Notions des langages de description d'architecture

Cette section présente au lecteur le domaine des langages de description d'architecture. Après avoir présenté le standard ISO/IEC/IEEE 42010 qui propose un ensemble de définitions liées au domaine, nous discutons des principales caractéristiques d'un ADL.

#### 2.1.1 Définition de la description d'architecture

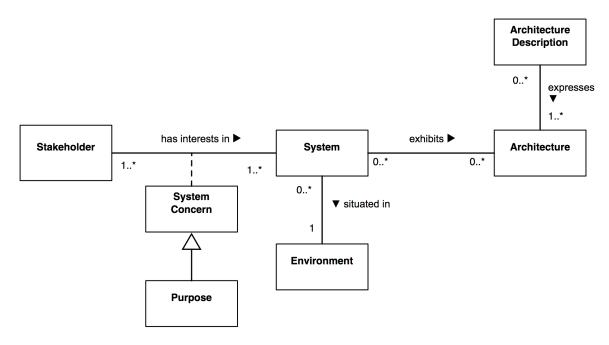

L'ISO/IEC/IEEE 42010 [42010, 2011] est un standard international intitulé Systems and software engineering - Architecture description<sup>1</sup>. Publié en 2011, il est le résultat d'une révision du standard IEEE Std 1471-2000 [Group, 2000] IEEE Recommended Pratice for Architectural Description of Software-Intensive Systems<sup>2</sup> réalisée conjointement par ISO et IEEE. Ce standard propose un ensemble de modèles conceptuels de définitions et de concepts ayant trait à l'AD. Ces modèles se présentent sous la forme de diagrammes de classes UML détaillant des classes d'entités et leurs relations. La figure 2.1 [42010, 2011]

<sup>1.</sup> Ingénierie des systèmes et des logiciels – Description de l'architecture

<sup>2.</sup> Pratiques recommandées par le IEEE pour la description architecturale des systèmes exigeant beaucoup de logiciels

présente le contexte de la description d'architecture. Les différentes entités sont détaillées ci-dessous.

Fig. 2.1 – Termes et concepts de la description d'architecture

System – Le standard ne définit pas précisément à quoi un *système* se rapporte. Il s'agit d'une abstraction permettant d'adapter l'AD au plus grand nombre de domaines. L'utilisateur de l'AD se charge de définir à quoi correspond le système dont il décrit l'architecture (ex. : une entreprise, un service, ou encore une application).

Environment – Tout système doit être considéré au sein d'un environnement qui l'influence. Ces influences peuvent être de tout ordre (politique, budgétaire, techniques, etc.) et ont un impact direct sur l'architecture à décrire. Ces influences ont pour nom concerns<sup>3</sup> dans le standard. Des centres d'intérêt possibles peuvent être : le coût, le besoin d'interopérabilité, la sécurité, etc.

Architecture – La définition donnée par le standard est concept fondamental ou propriétés d'un système, représenté au sein de son environnement, et incarné par ses élements, leurs relations, et par les fondements de leur conception et leur évolution. Un même système peut être représenté par une ou plusieurs architectures, et une architecture peut décrire un ou plusieurs systèmes selon le niveau d'abstraction.

Architecture description – Une description d'architecture est le produit d'un travail dont le but est d'exprimer l'architecture d'un système. Elle sert de base de référence aux parties prenantes et aux architectes pour comprendre, analyser et comparer des architectures. Une AD peut se présenter sous différentes formes : documents, ensemble de modèles, etc.

**Stakeholder** – Les *parties prenantes* caractérisent toute personne, groupe de personnes, ou organisation ayant des *centres intérêt* sur le système à décrire : client, propriétaire, architecte, développeur, etc.

<sup>3.</sup> Centres d'intérêt

#### 2.1.2 Définition de langage de description d'architecture

Le standard ISO/IEC/IEEE 42010 définit un langage de description d'architecture comme toute forme d'expression utilisée dans le contexte de la description d'architecture. Dans cette partie, nous détaillons les principaux objectifs d'un ADL dans le cadre de l'architecture logicielle, puis nous décrivons les principales caractéristiques de ce type de langage.

Pour Allen, un ADL a principalement 3 objectifs : 1) proposer une notation formelle claire et précise, 2) permettre l'analyse des systèmes décrits (si possible grâce à des outils automatisés), et 3) pouvoir s'adapter au vocabulaire de l'architecte [Allen, 1997].

Avant l'arrivée des ADLs, les systèmes étaient généralement décrits à l'aide de "diagrammes de boîtes et de flèches". Dans cette configuration, les concepts sont modélisés graphiquement et servent de référence aux parties prenants pour communiquer. Le problème avec ce mode de représentation non formelle est qu'il est soumis à l'interprétation des participants. Par conséquent, des erreurs de compréhension peuvent subvenir. Une méthode de notation claire et compréhensible par tous est rapidement devenue une nécessité.

L'utilisation d'une notation formelle induit la possibilité d'appliquer des outils automatisés pour réaliser diverses analyses et opérations sur les modèles exprimés. Par exemple, des parsers<sup>4</sup> peuvent être utilisés afin de détecter toute erreur de syntaxe sur les modèles, et des compilateurs peuvent servir à repérer des erreurs de sémantique. Des outils plus perfectionnés peuvent être utilisés pour des analyses plus poussées comme des tests d'ordonnançabilité (nous le verrons plus loin), ou encore pour générer du code exécutable à partir de modèles.

Enfin, comme nous l'avons précédemment expliqué, la description d'architecture ne se cantonne pas à un seul domaine. Il en est de même pour les ADLs. Ainsi, plus un ADL permettra à un architecte d'exprimer une architecture sans effort de traduction, plus il aura de chance d'être adopté et donc réutilisé.

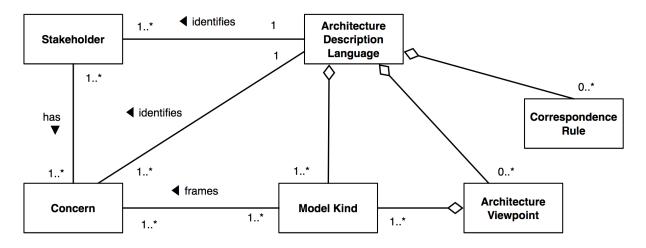

La figure 2.2 [42010, 2011] présente le contexte d'un langage de description d'architecture. Les différentes entités sont détaillées ci-dessous.

Fig. 2.2 – Termes et concepts des langages de description d'architecture

<sup>4.</sup> Outils d'analyses syntaxiques

Architecture viewpoint – Un point de vue d'architecture est un ensemble de conventions pour construire, interpréter, analyser et utiliser une vue d'architecture. Une vue d'architecture exprime l'architecture d'un système selon le point de vue d'une ou de plusieurs parties prenantes. Le point de vue d'architecture décrit entre autres : des types de modèles, des langages et des notations, des méthodes de modélisation et des techniques d'analyses permettant de cibler un ensemble d'intérêts précis.

Model kind – Un type de modèle définit les conventions d'un type de modèle d'architecture. Les vues d'architecture sont constituées d'un ou plusieurs modèles d'architecture. Ceux-ci fournissent des méthodes pour partager des détails entre vues d'architecture, et permettent aussi l'utilisation de plusieurs types de notations à l'intérieur d'une même vue.

Correspondence rule – Dans une description d'architecture, chaque entité est représentée par un élément. Chaque élément peut être en relation avec d'autres éléments, on parle alors de *correspondance*. Les correspondances sont notamment utilisées pour exprimer les relations d'intérêts à l'intérieur d'une ou de plusieurs descriptions d'architecture. Les *règles de correspondance* sont alors utilisées pour renforcer ces relations.

#### 2.1.3 Composition d'un langage de description d'architecture

Les blocs constitutifs d'un ADL sont les composants, les connecteurs, et les descriptions de configuration (ou déploiements). Tout ADL doit fournir des moyens pour pouvoir les spécifier explicitement. De plus, on attend d'un ADL qu'il soit fourni avec un ensemble d'outils permettant de réaliser des analyses plus ou moins complexes sur les modèles décrits. Ces outils peuvent par exemple proposer des fonctionnalités de spécification de modèles, de vues multiples, de génération de code, etc.

Les premiers langages de description d'architecture sont apparus au début des années 90 et se sont rapidement multipliés. Des tentatives de classification et de comparaison de ces langages ont alors été proposées afin de combler le manque de définition claire et précise. Parmi ces publications, nous pouvons citer celle de Nenad MEDVIDOVIC intitulée A Classification and Comparison Framework for Software Architecture Description Languages [Medvidovic, 1997]. Ce rapport technique propose une taxonomie détaillée afin de classer les fonctionnalités des ADLs. Quoique ancien, ce rapport est encore largement cité dans les publications associées au domaine de la description d'architecture.

Les composants — Un composant modélise une unité de calcul ou de stockage de données (ex. : une fonction procédurale, une application). Ils constituent les éléments centraux d'une architecture logicielle. Ils peuvent être simples ou bien composés d'un ensemble de sous-composants, on parle alors de *composite*. Un composant a les caractéristiques suivantes :

- une interface : l'ensemble des points d'interaction de ce composant avec le reste du monde ; spécifie les services offerts par le composant, ainsi que les services requis de la part des autres composants de l'architecture. Un point d'interface est généralement appelé un port.

- un **type** : le modèle abstrait à partir duquel il est possible d'instancier différentes implantations d'un même type de composant (améliore la réutilisabilité du composant dans les modèles).

<sup>5.</sup> Un cadre pour la classification et la comparaison des langages de description d'architecture logicielle

- une sémantique : dont le rôle consiste à compléter l'interface en enrichissant le modèle avec l'utilisation de propriétés afin de permettre des analyses plus fines, renforcer les contraintes, et assurer la cohérence du modèle sur différents niveaux d'abstraction.

- des **contraintes** : des propriétés et/ou assertions dont la violation rend le système décrit incompatible avec les attentes de ses parties prenantes (renforcement des conditions d'utilisation, établissement des dépendances entre sous-composants).

- une **évolutivité** : on attend d'un composant de pouvoir être réutilisé dans d'autres modèles (par des techniques comme le sous-typage ou le raffinement).

- des propriétés non fonctionnelles : des propriétés qui permettent notamment de simuler le comportement attendu du composant à l'exécution, de renforcer les contraintes, de préciser les critères de performances, etc.

Les connecteurs — Un connecteur modélise les interactions entre composants et les règles qui gouvernent ces interactions. Contrairement aux composants, les connecteurs ne sont pas traduits en unités de calcul dans le système implanté. Leur implantation peut prendre différentes formes : périphériques de routage de messages, variables partagées, mémoires tampons, structures de données dynamiques, etc. Un connecteur a les caractéristiques suivantes :

- une **interface** : l'ensemble des points d'interaction entre le connecteur et les composants auxquels il est lié. Ces points d'interface sont généralement appelés *pôles*. On distingue les *pôles d'entrée* des *pôles de sortie*.

- un type : le modèle abstrait à partir duquel il est possible d'instancier différentes implantations du même type de connecteur (améliore la réutilisabilité du connecteur dans les modèles). Les types de connecteur peuvent représenter les protocoles de communication.

- une sémantique : dont le rôle consiste à compléter l'interface en enrichissant le modèle avec l'utilisation de propriétés afin de permettre des analyses plus fines, renforcer les contraintes, et assurer la cohérence du modèle entre les différents niveaux d'abstraction.

- des **contraintes** : des propriétés et/ou assertions dont la violation rend le système décrit incompatible avec les attentes de ses parties prenantes (renforcement des conditions d'utilisation, établissement des dépendances entre sous-composants).

- une **évolutivité** : on attend d'un connecteur de pouvoir évoluer avec les mises à jour du protocole qu'il modélise (par des techniques comme le sous-typage, ou le raffinement).

- des propriétés non fonctionnelles : des propriétés qui permettent notamment de simuler le comportement attendu du connecteur à l'exécution, de renforcer les contraintes, de préciser des critères de performances, etc. Les propriétés non fonctionnelles d'un connecteur peuvent avoir une influence sur le choix du type de connecteur (ex. : bus de message) à implanter sur les processeurs.

Les descriptions de configuration — Une description de configuration correspond à un graphe connecté de composants et de connecteurs qui décrit la structure de l'architecture d'un système. Elle permet de déterminer si les composants appropriés sont bien connectés, si leurs interfaces correspondent, si les connecteurs supportent le bon protocole de communication, et si les sémantiques combinées fournissent le comportement attendu.

Une description de configuration a les caractéristiques suivantes :

- des **spécifications compréhensibles** : la compréhension des configurations facilite la communication entre les parties prenantes. Un syntaxe claire et précise couplée à un langage graphique interchangeable correspond à une solution pour répondre à cet objectif.

- une **hiérarchie de composants** : cette hiérarchisation permet de structurer l'architecture. La décomposition de l'architecture permet d'obtenir différents niveaux d'abstraction et donc une meilleure expressivité du modèle.

- une hétérogénéité des éléments : l'objectif des architectures logicielles est de faciliter le développement de systèmes de grande taille dans lesquels coexistent une grande variété de composants à la granularité variable, ainsi que des connecteurs décrivant différents protocoles de communication. La capacité d'un langage à représenter cette variété d'éléments améliore l'expressivité du modèle et permet de s'adapter à tous types de domaine.

- des contraintes : qui permettent de décrire les dépendances nécessaires entre composants et connecteurs au sein d'une configuration. Les contraintes de description de configuration permettent d'établir les contraintes locales du système.

- la capacité de raffiner le modèle et de tracer ces modifications : l'objectif d'un ADL est de décrire une architecture qui sera ensuite traduite en code exécutable.

Ceci est rendu possible par le raffinement progressif des composants jusqu'au niveau le plus élémentaire. Le traçage de ces raffinements permet la navigation entre les différents niveaux d'abstraction.

- la capacité de changer d'échelle, d'évoluer, et de dynamiser les modèles : les modèles ne sont pas statiques et évoluent en fonction des besoins (nouvelles spécifications, changement de protocole de communication, etc.). La possibilité de s'adapter à ces changements améliore la réutilisabilité des différents éléments.

- des propriétés non fonctionnelles : des propriétés qui permettent notamment de simuler le comportement attendu du système décrit, de renforcer les contraintes, de mapper les blocs d'architecture sur les processeurs, et d'aider à la gestion de projet.

Les outils de support — Les outils de support d'un ADL constituent sa valeur ajoutée. Ces outils sont destinés à réaliser différents types d'analyse, de vérification, de simulation, ou d'évaluation sur les performances. Plus que les possibilités offertes par le langage, c'est la présence et surtout la variété des fonctionnalités offertes par ses outils qui conditionnera l'adoption d'un ADL par les utilisateurs [Malavolta et al., 2013]. Les outils d'un ADL peuvent être classés par :

- la capacité de spécifier des architectures : plus qu'un simple éditeur de texte ou un outil de modélisation graphique, les outils doivent apporter des fonctionnalités d'aide à la notation (on peut distinguer les outils pro-actifs qui s'adaptent en fonction de l'état courant du modèle des outils réactifs qui détectent les erreurs au cours de la modélisation).

- la capacité de proposer différentes vues du même modèle : cela afin de permettre aux différentes parties prenantes d'intervenir sur le point qui les intéresse. Généralement, les outils proposent deux types de vue : textuelle et graphique. D'autres types de vue sont possibles : visualisation de la hiérarchie des composants, visualisation du processus de développement, visualisation animée du déroulement d'une simulation, etc

- les différents types d'analyse disponibles : ceux-ci doivent couvrir un large éventail

allant de la correction des erreurs de syntaxe (via des parsers) et de sémantique (via des compilateurs), à la prévention de deadlocks potentiels, ou bien la réalisation de tests de faisabilité.

- la cohérence du modèle à travers ses différents niveaux de **raffinement**.

- la génération de code : l'un des principaux objectifs des ADLs est de permettre la génération automatique de code à partir de modèle d'architecture. De cette manière, il est possible d'éviter les erreurs que le développeur pourrait introduire en implantant "à la main" un modèle. Cette fonctionnalité est retrouvée dans la plupart des frameworks d'ADLs (Aesop, C2, Darwin, Rapid, etc.).

- la capacité de gérer **dynamisme** des modèles.

#### 2.2 Présentation de AADL

La Society of Automotive Engineers (SAE) est une association internationale regroupant différents types d'acteurs du milieu automobile (étudiants, ingénieurs, chefs d'entreprise, etc.) qui échangent autour des idées relatives à l'automobile. En novembre 2004, elle publie le standard aérospatial AS5506 intitulé Architecture Analysis and Design Language<sup>6</sup>, ou AADL. Il s'agit d'un language de description d'architecture basé sur MetaH [Feiler et al., 2006]. AADL a été pensé pour permettre la représentation d'architectures de systèmes embarqués.

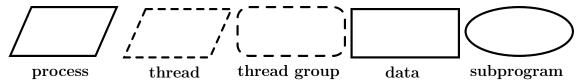

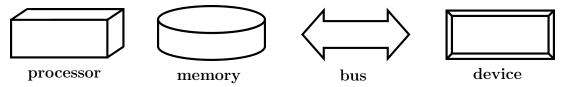

Une description d'architecture AADL différencie la partie logicielle de la partie matérielle d'un système. Côté logiciel, on peut distinguer les composants de type **process**, **thread**, **thread group**, **data**, et **subprogram**. Côté matériel, on distingue les composants de type **processor**, **memory**, **bus**, et **device**. Enfin, il existe le composant de type **system** qui correspond à un composite utilisé pour constituer des blocs logiques de sous-composants, et ainsi architecturer un modèle.

Cette partie traite des différents éléments du langage AADL, puis présente quelques outils se basant sur ce langage.

#### 2.2.1 Eléments du langage

Dans cette partie, nous détaillons les composants permettant de décrire la partie logicielle d'un système, puis ceux utilisés pour décrire la partie matérielle. Enfin, nous présentons le composant system.

**process** – Le composant process décrit un espace d'adressage protégé, un espace de partitionnement où tout ce qui est contenu est protégé des autres composants du système. Cet espace d'adressage contient :

- les images binaires exécutables (code exécutable et données) associées au process;

- les images binaires exécutables associées aux sous-composants du process;

- les sous-programmes offrant des services (code exécutable) et des données référencés par les composants externes.

Le composant process accepte 3 types de sous-composants : thread, thread group, et data. Contrairement à un processus POSIX, un process ne contient pas de thread de manière

<sup>6.</sup> Langage de conception et d'analyse d'architecture

implicite. Pour représenter un composant actif, il est nécessaire de déclarer un thread, ou un thread group, comme sous-composant du process.

thread – Le composant thread décrit un composant actif (comme un thread POSIX). Les threads AADL peuvent avoir différents modes opératoires. Chaque mode peut décrire un comportement et des valeurs de propriétés différentes. Le composant thread n'accepte qu'un seul type de sous-composant : data. Il est possible de déclarer un appel à un subprogram <sup>7</sup>.

thread group — Le composant thread group décrit un composant abstrait regroupant un ensemble de threads, de data, et de thread groups au sein d'un process. Les thread groups offrent une séparation des points d'intérêts en définissant une référence unique à un ensemble de threads et de data. Le composant thread group accepte 3 types de sous-composants : thread, thread group, et data

**data** – Le composant data représente des données statiques (ex : des données numériques, un texte source) et des types de données d'un système. Les déclarations de composant data sont notamment utilisées pour représenter :

- les types de données d'une application (ex. : types de données échangées entre les ports, paramètres);

- les sous-structures de types de données (par composition);

- les instances de données.

Le composant data n'accepte qu'un seul type de sous-composant : data. Il est donc possible de déclarer des structures hiérarchiques de données.

subprogram — Le composant subprogram représente un code source exécutable de manière séquentielle, c'est-à-dire un composant pouvant être invoqué avec ou sans paramètre, et qui travaille sur des données ou fournit des fonctionnalités aux composants qui l'utilisent. La signature du subprogram et de ses paramètres est déclarée comme sous-composant. Seuls le thread et le subprogram peuvent déclarer un appel à un subprogram. Le composant subprogram ne peut pas contenir de sous-composant.

Fig. 2.3 – Représentation graphique des composants logiciels AADL

**processor** – Le composant processor est une abstraction du matériel et de la partie applicative associée responsable de l'ordonnancement et de l'exécution d'un ensemble de threads. Il peut embarquer une partie logicielle (ex. : un système d'exploitation) chargée de l'ordonnancement ainsi que d'autres fonctionnalités destinées au support des threads. Le composant processor n'accepte qu'un seul type de sous-composant : memory.

<sup>7.</sup> Sous-programme

memory – Le composant memory représente un composant de stockage de données ou de code exécutable. Il peut représenter une mémoire à l'intérieur d'un processor ou d'une unité de plateforme d'exécution séparée. Une mémoire est connectée à un processor via un bus. Le composant memory n'accepte qu'un seul type de sous-composant : memory.

bus — Le composant bus représente le matériel et les protocoles de communication associés qui rendent possibles les interactions entre les composants d'une plateforme d'exécution (c.-à-d. : memory, processor, et device). Les bus peuvent être connectés directement à d'autres bus pour représenter des communications complexes entre réseaux. Le composant bus ne peut pas contenir de sous-composant.

**device** – Le composant device représente une entité qui sert d'interface entre une application système et l'environnement extérieur. Les devices peuvent avoir des comportements complexes et contenir des composants matériels qui ne sont pas représentés explicitement dans le modèle. Le composant device ne peut pas contenir de sous-composant.

Fig. 2.4 – Représentation graphique des composants matériels AADL

system - Le composant system est un composite qui peut contenir des composants logiciels, matériels, ou systèmes. Ce type de composant est utilisé afin de faciliter la représentation hiérarchique des composants d'une architecture. Le composant system est placé tout en haut de la hiérarchie des composants; il peut donc accepter les sous-composants suivants : data, process, processor, memory, bus, device, et system.

Fig. 2.5 – Représentation graphique du composant AADL system

#### 2.2.2 Extension du langage

Il est possible d'étendre le langage de base par la déclaration de bibliothèques d'annexes. Ces extensions permettent notamment de réaliser des analyses personnalisées via l'utilisation de modèles et d'abstractions spécialisés [Bozzano et al., 2010].

#### 2.2.3 Quelques outils

Dans cette partie, nous présentons quelques outils existants pour réaliser des modèles AADL ainsi que différents types d'analyse.

Stood – Stood est un outil de modélisation qui supporte le langage AADL. De plus, il permet d'appliquer la méthodologie HOOD <sup>8</sup> [Dissaux and Singhoff, 2008]. HOOD est une méthode de modélisation créée par l'Agence Spatiale Européenne en 1987. Elle permet de décomposer un problème logiciel en une hiérarchie d'objets, de classes, et d'opérations. La méthologie propose entre autres un langage textuel et un langage graphique. Avec Stood, il est possible de gérer complètement un projet logiciel en construisant des bibliothèques de composants réutilisables, de faire du rétro-engineering de code, et de modéliser une application temps-réel et sa plateforme d'exécution. Stood propose aussi une fonctionnalité de génération de code AADL à partir des modèles spécifiés.

Ocarina — Ocarina est une suite d'outils développée par Télécom Paris. Cette application est construite autour d'un noyau qui fournit un ensemble de fonctionnalités de manipulation de modèles AADL. Parmi ces fonctionnalités, on peut notamment citer l'analyse syntaxique et la représentation graphique de modèles AADL (utilisation de Dia), ainsi que des fonctionnalités de génération de code pouvant être déployé sur différentes plateformes.

Cheddar – Cheddar est un framework qui fournit des outils de simulation permettant de réaliser des tests selon différents critères de performances (contraintes temporelles, dimensionnement des ressources, etc.) [Singhoff et al., 2004]. Cheddar se base entre autres sur la théorie d'ordonnancement temps-réel pour évaluer si un système répond à un ensemble de contraintes temporelles. Il est possible de spécifier une application en déclarant un ensemble de processeurs, de tâches, de buffers, de ressources partagées, et de messages. Des tests de faisabilité peuvent alors être réalisés. Cheddar v3 propose une fonctionnalité de parsing de modèles AADL v1. Il est donc possible de charger un modèle d'application AADL et de réaliser des simulations sur l'ordonnancement de ce modèle.

AADLInspector – AADLInspector est un framework de traitement de modèles AADL développé et édité par la société Ellidiss. Son objectif est de fournir une solution légère et évolutive permettant de réaliser des analyses statiques et dynamiques d'architectures écrites en AADL, et de se connecter facilement sur des outils de vérification de code AADL ou de génération de code exécutable compatibles. AADLInspector se base sur le moteur de Cheddar v3 pour réaliser des tests de faisabilités et des simulations d'ordonnancement. Il rend aussi possible l'analyse de modèles AADL v2 grâce à un outil de formattage embarqué qui transforme du code AADL v2 en code AADL compatible Cheddar v3.

OSATE — Osate est un plugin Eclipse permettant de gérer des projets de modélisation AADL. Gratuit, il permet de rapidement créer des modèles AADL v2, et propose un ensemble d'outils d'analyse comme un parser syntaxique ou un analyseur sémantique. Il propose aussi une fonctionnalité de modélisation passant par la notation graphique du langage AADL. Parmi les autres fonctionnalités offertes par Osate, nous pouvons citer un outil d'analyse de flux de données. Les flux de données permettent de décrire une communication bout-à-bout entre composants d'un modèle [Hudar and Feiler, 2007]. Il est donc possible de réaliser des tests sur les temps de transmission d'un message à travers tout un système.

<sup>8.</sup> Hierarchic Object-Oriented Design

#### 2.3 Théorie d'ordonnancement temps-réel

John Stankovic <sup>9</sup> propose la définition suivante pour décrire un système temps-réel : Les systèmes temps-réel sont des systèmes pour lesquels l'exactitude ne se mesure pas seulement sur les résultats des calculs logiques, mais aussi sur le temps sur lequel ces résultats sont produits [Stankovic, 1988]. La théorie de l'ordonnancement temps-réel regroupe un ensemble d'algorithmes permettant de déterminer la manière selon laquelle un ensemble de tâches se partagent du temps de calcul. Elle propose aussi un ensemble de méthodes analytiques appelées tests de faisabilité et tests d'ordonnancement. Ces tests sont utiles pour déterminer le comportement d'un système avant son implantation/exécution [Singhoff, 2014].

Après avoir présenté le modèle canonique d'une tâche, nous donnons un aperçu des outils mis à disposition des architectes système par la théorie d'ordonnancement temps-réel.

#### 2.3.1 Modèle canonique d'une tâche

Une tâche est constituée d'une séquence d'instructions, d'un ensemble de données, et d'un contexte d'exécution. On distingue principalement 2 types de tâches : les tâches périodiques et apériodiques. Dans un système temps-réel, ce sont les tâches périodiques qui sont considérées comme critiques. Par conséquent, il est important d'en satisfaire les propriétés d'ordonnancement.

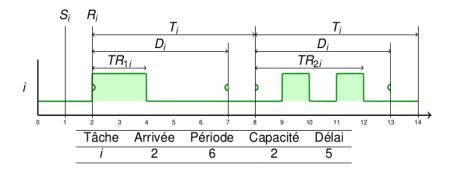

Une tâche i, qu'elle soit périodique ou apériodique, possède un ensemble de propriétés d'ordonnancement :

- une date d'arrivée dans le système  $S_i$ ;

- une date de premier déclenchement  $R_i$ ;

- une période d'activation  $P_i$  qui correspond au temps écoulé entre deux déclenchements de la tâche;

- une deadline  $D_i$  qui correspond au délai maximum acceptable pour son exécution;

- une capacité  $C_i$  qui correspond au pire temps CPU nécessaire à son exécution;

- une priorité utilisée par l'ordonnanceur pour sélectionner la tâche parmi les tâches disponibles.

La figure 2.6 [Pouiller, 2011] permet de visualiser ces différentes propriétés.

La théorie d'ordonnancement temps-réel propose plusieurs méthodes pour attribuer une priorité à une tâche d'un système. Par exemple, il est possible de se baser sur la criticité ou l'urgence de la tâche. On peut aussi considérer les dépendances entre tâches et faire en sorte qu'une tâche qui a besoin du résultat d'une autre tâche possède une priorité moins élevée. Il existe aussi plusieurs algorithmes d'ordonnancement parmi lesquels nous pouvons citer **Rate-Monotonic** [Liu and Layland, 1973], **Early Deadline First** (EDF), **FIFO**, **LIFO**, et **Round-Robin**. Rate-Monotonic est généralement utilisé dans les problématiques d'ordonnancement à priorité fixe.

<sup>9.</sup> Professeur à l'Université du Massachussets de Amherst qui a beaucoup travaillé sur les systèmes temps-réel

Fig. 2.6 – Propriétés d'ordonnancement d'une tâche

#### 2.3.2 Méthodes de vérification de l'ordonnançabilité d'un système

La théorie d'ordonnancement propose un ensemble de méthodes afin de tester l'ordonnançabilité d'un système. Dans le cadre de l'ordonnancement à priorité fixe dans un système préemptif, le calcul du taux d'occupation du processeur est suffisant pour vérifier si un jeu de tâches donné est ordonnançable. Le calcul du pire temps d'exécution ou encore la simulation d'ordonnancement sur la période fondamentale (aussi appelée *hyperpériode*) peuvent aussi être utilisés pour vérifier l'ordonnançabilité d'un système.

La méthode du calcul du taux d'occupation du processeur [Liu and Layland, 1973] est une méthode utilisée pour vérifier l'ordonnançabilité d'une tâche. Elle repose sur l'équation

$$U = \sum_{i=1}^{n} \frac{C_i}{P_i} \le n \left( 2^{\frac{1}{n}} - 1 \right) \tag{2.1}$$

où n est le nombre de tâches du système,  $C_i$  est la capacité de la tâche i, et  $P_i$  est période de la tâche i. La validation de cette équation est une condition suffisante pour confirmer l'ordonnançabilité d'un système.

Le calcul du pire temps d'exécution d'une tâche [Audsley et al., 1993] permet de déterminer le délai entre l'activation d'une tâche et sa terminaison. Un jeu de tâches est ordonnançable si toutes les échéances sont respectées. Cette méthode repose sur l'équation

$$r_i = C_i + \sum_{j \in hp(i)} \left\lceil \frac{r_i}{P_j} \right\rceil C_j \tag{2.2}$$

où  $r_i$  est le pire temps de réponse de la tâche i,  $C_i$  est la capacité de la tâche i, hp(i) est l'ensemble des tâches qui ont une plus grande priorité que la tâche i,  $C_j$  est la capacité de la tâche j, et  $P_j$  est la période de la tâche j. L'évaluation des temps d'exécution d'un jeu de tâches est une condition suffisante et nécessaire pour vérifier l'ordonnançabilité d'un système.

#### Simulation d'ordonnancement sur l'hyperpériode

L'hyperpériode (ou période fondamentale) correspond au plus petit multiple commun de toutes les périodes d'un jeu de tâches. La simulation de l'ordonnancement d'un jeu de tâches sur l'hyperpériode permet d'avoir les résultats exacts du comportement du système et constitue une condition nécessaire et suffisante pour en vérifier l'ordonnançabilité.

#### 2.4 Description d'architecture et qualification temps-réel

Dans cette partie, nous présentons trois travaux proposant des solutions différentes pour qualifier temporellement un système décrit en langage AADL. Le premier travail décrit une méthode de traduction de modèles AADL en modèles BIP pour utiliser les fonctionnalités offertes par le framework BIP. Le deuxième travail s'intéresse à la notion de flux afin d'évaluer le temps de communication bout-à-bout d'un message dans un système composé de plusieurs composants. Enfin, le dernier travail présente une méthode qui se base sur l'utilisation de Cheddar pour réaliser des tests de faisabilité sur un système décrit à partir du langage AADL.

Le sujet de thèse de Mohamed Y. Chkouri a porté sur la définition d'une méthodologie de traduction de modèles AADL en langage BIP <sup>10</sup> [Chkouri, 2010]. BIP est un framework utilisé pour décrire des architectures rigoureuses. En plus d'un langage spécifique, il fournit un ensemble d'outils permettant de construire des systèmes complexes en associant le comportement d'un ensemble de composants atomiques. Ce comportement est décrit comme un réseau de Petri étendu avec des données et des fonctions écrites en langage C. BIP dispose notamment d'un moteur temps-réel qui exécute des programmes BIP sur une plateforme cible. La transformation du modèle AADL en description BIP est réalisée grâce à une extension de la syntaxe du langage AADL spécialement créée. Chkouri valide sa méthodologie à travers un exemple de traduction d'un modèle AADL d'ordinateur de vol.

Dans leur guide pratique sur la création de modèles AADL pour les systèmes de contrôle, John Hudak et Peter Feiler proposent d'utiliser les flux AADL pour évaluer le temps de communication bout-à-bout d'une information [Hudar and Feiler, 2007]. Pour décrire cette méthode, ils proposent de considérer un modèle de système de contrôle d'un véhicule. Les flux sont des outils du langage AADL permettant d'introduire les notions de flow source 11, flow path 12, et de flow sink 13. Ainsi, il est possible de considérer la transmission d'une information à travers un ensemble de composants, et de réaliser des mesures sur les temps de transmission. Ce guide permet aussi de découvrir certaines fonctionnalités offertes par le framework Osate en ce qui concerne l'étude des flux d'un système. L'avantage de cette méthode est qu'il est possible de regrouper l'ensemble des opérations de modélisation et d'évaluation au niveau d'un seul outil : Osate.

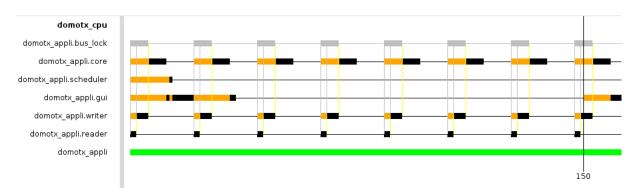

Dans leur publication Développement de systèmes à l'aide d'AADL – Ocarina/Cheddar, Jérome Hugues et Frank Singhoff proposent une méthode de caractérisation temps-réel de modèles utilisant les outils Ocarina et Cheddar [Hugues and Singhoff, 2009]. Cette approche consiste à construire le modèle AADL d'un système, et à réaliser des analyses d'ordonnancement à partir de Cheddar. Cheddar permet de compléter la description des propriétés d'ordonnancement des entités du modèle grâce au **property set** Cheddar\_Properties. Cheddar intègre un analyseur de modèles AADL qui se base sur Ocarina. Il fournit ses résultats d'analyse de l'ordonnancement dans une fenêtre comportant deux parties : un chronogramme décrivant l'ordonnancement des threads pendant l'exécution du système, et les différents critères de performances (temps de réponse des threads, délais maximaux d'attente pour l'accès aux ressources partagées, etc.). L'exemple

<sup>10.</sup> Behavior Interaction Priority

<sup>11.</sup> Source du flux

<sup>12.</sup> Parcours du flux

<sup>13.</sup> Réceptacle du flux

donné se base sur la définition d'un modèle de radar constitué de plusieurs composants : un processeur et un processus hébergeant plusieurs threads.

Dans le cadre de cet état de l'art, nous n'avons pas trouvé de publication traitant de la description d'architecture de système domotique dans une optique de caractérisation des contraintes temporelles.

#### 2.5 Conclusion

Nous avons pu voir que la description d'architecture regroupe un grand nombre de concepts et permet de s'adapter à tout type de domaine. AADL, un langage de description d'architecture, permet de décrire des modèles de systèmes temps-réel grâce à la distinction des parties matérielle et logicielle. Les outils développés autour de ce langage autorisent toutes sortes d'analyses, notamment des analyses de l'ordonnancement. Dans le cadre de ce stage, il a été décidé de se concentrer sur l'outil Cheddar pour analyser un modèle de contrôleur central de réseau domotique.

## 3

### Modélisation du contrôleur domotique avec AADL

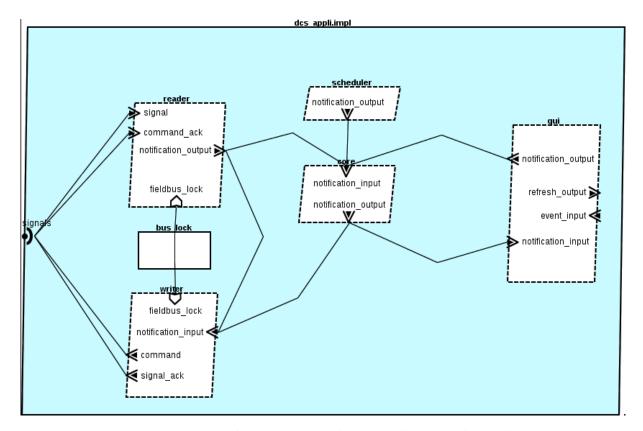

Ce chapitre présente le travail de modélisation du contrôleur central du réseau domotique imaginé par Tréflévénet. Ce travail consiste à concevoir une architecture du contrôleur central qui répondra à l'ensemble des besoins fonctionnels et non fonctionnels définis.

Dans une première partie, nous présentons le système considéré et donnons l'ensemble des besoins fonctionnels et non fonctionnels attendus pour le contrôleur central. Dans une seconde partie, nous décrivons le travail de modélisation réalisé avec le langage AADL.

#### 3.1 Description du système domotique

En ingénierie des systèmes, la conception d'un système démarre par la prise en compte des exigences fonctionnelles et non fonctionnelles. Les exigences fonctionnelles décrivent les fonctions que doit réaliser le système. Elles décrivent son comportement externe, et permettent au client et à l'ingénieur système de s'engager sur un périmètre et un ensemble de conditions à satisfaire. Les exigences non fonctionnelles sont toutes les spécifications qui n'expriment pas une fonction du logiciel. On distingue généralement deux types : les contraintes d'interface (environnement matériel, etc.) et les contraintes de performances (mémoire, disque, réactivité, etc.).

Cette section présente les spécifications du contrôleur central d'un réseau domotique. Dans une première partie, nous décrivons le réseau domotique imaginé par l'association Tréflévénet et nous positionnons le contrôleur central au sein de ce système. Puis nous détaillons les fonctionnalités que devra remplir ce contrôleur. Enfin, nous discutons des besoins non fonctionnels, et en particulier des contraintes temporelles à appliquer sur le contrôleur.

#### 3.1.1 Réseau domotique considéré

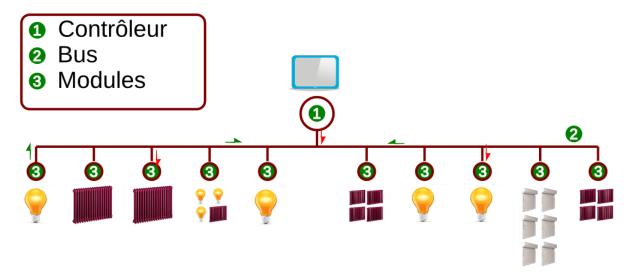

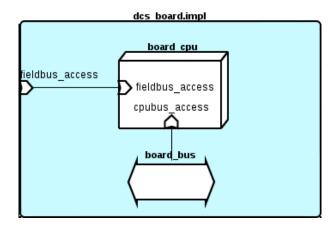

Le réseau domotique est constitué d'un bus de terrain, d'un ensemble de modules esclaves, et d'un contrôleur central. Le contrôleur et chaque module sont connectés sur le bus de terrain à travers lequel ils échangent des messages. La figure 3.1 présente une vue simplifiée du réseau domotique.

Fig. 3.1 – Architecture du système domotique

Le bus de terrain est le système d'interconnexion qui relie les modules esclaves au contrôleur central. Il repose sur une liaison série de type RS-485 configurée de 9600 bauds à 115200 bauds. Le tableau 3.1 présente les résultats de l'évaluation des débits et vitesses de transmission réalisée sur ce bus pour une configuration classique 8N1. Sachant que le protocole de communication spécifie une taille maximale de 20 octets pour les messages transitant sur le bus, on peut donc en déduire que le pire temps de propagation d'un message oscille entre 1.8 ms et 20.8 ms.