# The Esterel v5 Language Primer Version 5.21 release 2.0

Gérard Berry Centre de Mathématiques Appliquées Ecole des Mines and INRIA 2004 Route des Lucioles 06565 Sophia-Antipolis

berry@sophia.inria.fr

April 6, 1999

# Contents

| Pı | Preface 1                                                                |      |  |

|----|--------------------------------------------------------------------------|------|--|

| 1  | Deterministic Reactive Systems                                           | 9    |  |

|    | 1.1 Transformational, Interactive, and Reactive Systems                  | . 9  |  |

|    | 1.2 Control-Dominated Reactive Systems                                   |      |  |

|    | 1.3 Determinism Versus Non-Determinism                                   |      |  |

|    | 1.4 Programming Tools                                                    | . 12 |  |

| 2  | The Esterel Programming Style                                            | 15   |  |

|    | 2.1 Pure Signal Handling: the ABRO example                               | . 15 |  |

|    | 2.1.1 Execution Traces                                                   |      |  |

|    | 2.1.2 Mealy Machines                                                     | . 17 |  |

|    | 2.1.3 ABRO in Esterel                                                    | . 17 |  |

|    | 2.2 Write Things Once                                                    | . 20 |  |

|    | 2.3 Valued signals: the SPEED example                                    |      |  |

|    | 2.3.1 Valued Signals Versus Variables                                    | . 23 |  |

|    | 2.4 Weak and Immediate Abortion                                          | . 25 |  |

|    | 2.5 Using Submodules: the REGUL Specification                            | . 28 |  |

|    | 2.6 Suspension                                                           | . 29 |  |

|    | 2.7 Generic Behaviors and Modules                                        | . 31 |  |

|    | 2.8 Multiform Time                                                       | . 33 |  |

|    | 2.8.1 The RUNNER example                                                 | . 34 |  |

|    | 2.9 Traps and Exception Handling                                         | . 35 |  |

|    | 2.10 Boolean Signal Expressions and the Present Test $\ \ldots \ \ldots$ | . 37 |  |

| 3  | A Tour of Esterel                                                        | 41   |  |

|    | 3.1 Lexical Aspects                                                      | . 41 |  |

|    | 3.2 Modules                                                              | . 41 |  |

|    | 3.3 Data                                                                 | . 43 |  |

ii CONTENTS

|   |     | 3.3.1   | Types and Operators                           |

|---|-----|---------|-----------------------------------------------|

|   |     | 3.3.2   | Constants                                     |

|   |     | 3.3.3   | Functions                                     |

|   |     | 3.3.4   | Procedures                                    |

|   |     | 3.3.5   | Tasks                                         |

|   | 3.4 | Signals | s and Sensors                                 |

|   |     | 3.4.1   | Interface Signal Declarations                 |

|   |     | 3.4.2   | Single and Combined Valued Signals            |

|   |     | 3.4.3   | Sensors                                       |

|   |     | 3.4.4   | Input Relations                               |

|   |     | 3.4.5   | Local Signal Declaration                      |

|   | 3.5 | Variab  |                                               |

|   | 3.6 | Expres  | ssions                                        |

|   |     | 3.6.1   | Data Expressions                              |

|   |     | 3.6.2   | Signal Expressions                            |

|   |     | 3.6.3   | Delay Expressions                             |

|   | 3.7 | Staten  | nents                                         |

|   |     | 3.7.1   | Basic Control Statements                      |

|   |     | 3.7.2   | Assignment and Procedure Call                 |

|   |     | 3.7.3   | Signal Emission                               |

|   |     | 3.7.4   | Sequencing                                    |

|   |     | 3.7.5   | Looping                                       |

|   |     | 3.7.6   | Repeat Loops                                  |

|   |     | 3.7.7   | The present Signal Test                       |

|   |     | 3.7.8   | The if Data Test                              |

|   |     | 3.7.9   | The await Statement                           |

|   |     | 3.7.10  | The abort Statements                          |

|   |     | 3.7.11  | Temporal Loops                                |

|   |     | 3.7.12  | The suspend Statement                         |

|   |     | 3.7.13  | Traps                                         |

|   |     | 3.7.14  | The Parallel Statement                        |

|   |     | 3.7.15  | The run Module Instantiation Statement        |

|   |     | 3.7.16  | The exec Task Execution Statement             |

| L | Cor | struct  | ive Causality 7                               |

|   | 4.1 |         | ${f urnation}$                                |

|   | 4.2 | Constr  | ructive Causality                             |

|   |     | 4.2.1   | Non-Reactive and Non-Deterministic Programs ' |

|   |     | 4.2.2   | Logical Correctness                           |

|   |     | 4.2.3   | Constructiveness                              |

| iii |

|-----|

| ii  |

|   |      | 4.2.4   | Constructiveness vs. Acyclicity                |

|---|------|---------|------------------------------------------------|

| 5 | Refl | ection  | on Perfect Synchrony 89                        |

|   | 5.1  |         | ve Programming Models                          |

|   |      | 5.1.1   | The Qualities of a Model 89                    |

|   |      | 5.1.2   | The Models of Esterel                          |

|   |      | 5.1.3   | Inter-Model Consistency 91                     |

|   |      | 5.1.4   | High-Level vs. Low-Level Programming Models 91 |

|   | 5.2  | Logica  | l Time vs. real Time                           |

|   | 5.3  | Implen  | nentation by Sequential Circuits 94            |

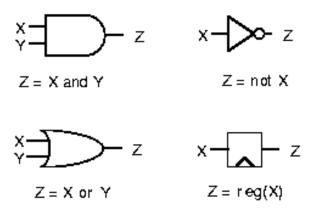

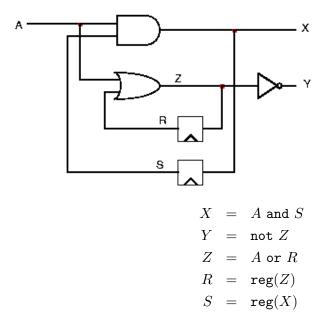

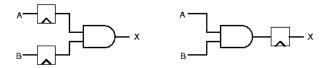

|   |      | 5.3.1   | The Logical View of Circuits 94                |

|   |      | 5.3.2   | The Electrical View of Circuits 95             |

|   |      | 5.3.3   | Connecting the Logical and Electrical Views 96 |

|   | 5.4  | Softwa  | re Implementation                              |

| 6 | The  | Ester   | el Grammar 99                                  |

|   | 6.1  | Syntax  | Notation                                       |

|   | 6.2  | Modul   | es                                             |

|   | 6.3  | Interfa | ce Declaration                                 |

|   |      | 6.3.1   | Type Declarations                              |

|   |      | 6.3.2   | Constant Declarations                          |

|   |      | 6.3.3   | Function Declarations                          |

|   |      | 6.3.4   | Procedure Declarations                         |

|   |      | 6.3.5   | Task Declarations                              |

|   |      | 6.3.6   | Signal Declarations                            |

|   |      | 6.3.7   | Sensor Declarations                            |

|   |      | 6.3.8   | Input Relation Declarations                    |

|   | 6.4  | _       | sions                                          |

|   |      | 6.4.1   | Data Expressions                               |

|   |      | 6.4.2   | Signal Expressions                             |

|   |      | 6.4.3   | Delay Expressions                              |

|   | 6.5  | Statem  |                                                |

|   |      | 6.5.1   | Signal Emission                                |

|   |      | 6.5.2   | Assignment and Procedure Call 109              |

|   |      | 6.5.3   | The present Signal Test                        |

|   |      | 6.5.4   | The if Data Test                               |

|   |      | 6.5.5   | Looping                                        |

|   |      | 6.5.6   | Repeat Loops                                   |

|   |      | 6.5.7   | The abort Statements                           |

|   |      | 6.5.8   | The await Statement                            |

iv CONTENTS

|     | 6.5.9  | Temporal Loops                         |

|-----|--------|----------------------------------------|

|     | 6.5.10 | The suspend Statement                  |

|     | 6.5.11 | Traps                                  |

|     | 6.5.12 | The exec Task Execution Statement      |

|     | 6.5.13 | Local Signal Declaration               |

|     | 6.5.14 | Local Variable Declaration             |

|     | 6.5.15 | The run Module Instantiation Statement |

| 6.6 | Old Sy | mtax                                   |

# **Preface**

This document is the primer for the ESTEREL<sup>TM</sup> synchronous programming language, which is devoted to programming control-dominated software or hardware reactive systems. The language version is that of the ESTEREL v5 system, but the language proper is in no way bound to that system, and this document should be valid for other implementations.

We tried to write the primer in a precise but informal way that should make most users happy in their use of the language and system. However, the primer is not meant to be the reference document for the language and semantics. The language reference manual will be appended to the primer in a subsequent release and the formal semantics is given in the companion book "The Constructive Semantics of Pure Esterel" [8], which discusses all mathematical semantics issues in depth. The use of the ESTEREL V5 system is presented in the documentation delivered with the system.

# Organization of the Primer

Chapter 1, Deterministic Reactive Systems, describes the systems to which ESTEREL is dedicated. Chapter 2, The Esterel Programming Style, illustrates ESTEREL programming by examples. Chapter 3, A Tour of Esterel, presents all the ESTEREL constructs. Chapter 4, Constructive Causality, studies semantical issues related to program correctness. Chapter 5, Reflections on Perfect Synchrony, reflects on the semantical model of ESTEREL and on its practical meaning. Chapter 6 presents the ESTEREL grammar and some old syntax that can still be used for backwards compatibility reasons.

#### The Evolution of Esterel

The Esterel language is both stable and in constant evolution. In its development, we always tried to conciliate two objectives:

- Keeping the language stable, to guarantee that already written programs compile without modification and that the compiled code can also be used without modification in its original execution environment.

- Making the language evolve, to follow the progress in the scientific knowledge on which it is grounded, to make it more more powerful, and, above all, to make it more user-friendly

To us, it is right to ask users to recompile their programs to benefit of new compiler versions that correct bugs or produce better code. It is much more questionable to ask them to rewrite or even adapt existing programs that have been extensively and carefully tested and verified, especially in the context of critical applications. All programs that have been written since 1985 (i.e. for the ESTEREL V2, V3, and V4 systems) still compile in a compatible way, but much more efficiently.

As far as evolution is concerned, new statements have been added over the years, such as the exec external task execution statement, and the syntax has been improved. For example, we now suggest to replace the "do...watching" statement by "abort...when" that is clearer and extends more naturally into "weak abort...when" that has been long missing. This document will always use the new syntax and it will mention the old syntax only for compatibility with the past.

The semantics has never "changed" in the sense that all programs that used to compile still do and keep the same semantics. However, the introduction of the *constructive semantics* has made the ground very firm and has solved many of the annoying problems encountered by users of previous versions that sometimes unduly rejected correct programs. The constructive semantics is informally presented here, see [8] for the formal presentation.

Our conservative politics has two obvious drawbacks: evolution is slowed down, and design mistakes must be faithfully carried over from a version to the next one. To reduce the number of mistakes, we introduced new constructs only when we thought we really understood all the transitive consequences of our choices and all the interactions between them. We were reasonably successful as far as executable statements are concerned, but

much less for the module structure that will require a deep revision to be really usable for big programs<sup>1</sup>.

Every language is a compromise; the best a language can do is to be transparent, i.e. to let the user reflect its way of thinking in the most direct and elegant way. Since this goal is highly unreachable, users usually complain about languages, even if they like them. Complaints about Esterel should be addressed to esterel-users@cma.inria.fr. Complaints about Esterel v5 system bugs should be addressed to esterel-bugs@cma.inria.fr.

### A Brief History of Esterel

In 1982, Jean-Paul Marmorat and Jean-Paul Rigault, two researchers in Control Theory and Computer Science at CMA  $^2$ , were designing a robot car for a race organized by an early microcomputer journal. They rapidly understood that the tools they had for programming the car were very far from being satisfactory. Classical languages did not let them express control algorithms in the way they were thinking about them. They recognized the need for specific statements to deal with time, namely delays and preemption, and they made the point that the repetition of any signal should count as an autonomous time unit. They drafted a little language using intuitive keywords. At that time, the author was working on theoretical aspects of  $\lambda$ -calculus and denotational semantics. He found the application area and the new ideas interesting and challenging, and he tried to make mathematical sense out of the language proposal.

With Sabine Moisan — who found the name ESTEREL<sup>3</sup> — and Jacques Camerini, we sorted out the primitives and we tried to use the newly developed SCCS and Meije synchronous process calculi to give their semantics (SCCS [41] is due to Robin Milner and Meije [3] to Gérard Boudol). The reference [14] is the oldest one about ESTEREL.

Process calculi turned out not to be well-adapted to ESTEREL. Fortunately, Gordon Plotkin published his seminal book on Structural Operational Semantics or SOS [44]. This new semantics style gave us much sharper tools to describe intrinsic semantics, and, above all, it freed us from the clas-

<sup>&</sup>lt;sup>1</sup>At the times where ESTEREL was designed, modules were not very well understood altogether, and we could not figure out what was the right choice. Then, causality issues attracted our attention and energy much more than a redesign of modules.

<sup>&</sup>lt;sup>2</sup>Centre de Mathématiques Appliquées, Ecole des Mines de Paris, Sophia-Antipolis

$<sup>^3</sup>$ The Estérel is a small but beautiful mountain range of red rocks culminating at 619 m, between Cannes and St Raphaël; "-terel" sounds a little bit like "temps-réel", which is real-time in French.

sical vision of concurrency as bound to interleaving and rendezvous communication, which was inappropriate in our control world. Laurent Cosserat and the author worked out a better set of primitives and made much better sense of instantaneous control propagation and communication, which is the key to get ESTEREL right[11, 24]. The author rediscovered the beautiful derivative algorithm of Brzozowski that translates any kind of regular expression into automata [20] and that can be extended to any finite-state language described by SOS rules. Using this algorithm, Laurent Cosserat wrote the first ESTEREL V1 prototype compiler to automata. That compiler was entirely rewritten by Philippe Couronné and the author in 1985-86, and the new ESTEREL V2 system was swiftly used for non-trivial academic and industrial applications.

Georges Gonthier's thesis [27] was a major step in the development of ESTEREL. He understood the fundamental distinction between the behavioral semantics, which is of a logical nature and based on mutual agreement about signal presence and values, and causality issues that deal with effective information propagation. He introduced the fundamental encoding of synchronization and exception by integers, and he designed much more efficient operational semantics and compiling algorithms. While the ESTEREL V2 compiler strictly used Brzozowski's original derivative algorithm in which automaton states are program texts, which is unreasonably memory-consuming, Gonthier's technique uses simple bit-sets as states, which is orders of magnitude more efficient (see [15] for the same kind of optimization for regular expressions). Finally, Gonthier designed the overall architecture of the ESTEREL V3 compiler, which was written in 1987-88 by Raphaël Bernhard, the author, Frédéric Boussinot, Annie Ressouche, Jean-Paul Rigault, and Jean-Marc Tanzi. The architecture and some intermediate codes have been kept basically unchanged since then. Esterel v3 has been used rather heavily. It worked well for small to medium-size programs, but blew up or big programs for which state space explosion turned out to be the rule.

The next progress came from interaction with Jean Vuillemin's group at Digital Equipment Paris Research Laboratory. This group was developing the PeRLe FPGA-based programmable hardware machine [16]. Many of the hardware designs involved controllers that are a pain in the neck to write with gates and registers, and the group thought that ESTEREL was very well adapted for direct controller specification. The author learned about logic and hardware and developed a structural translation of ESTEREL programs into gates that could be used to directly generate netlists, fully avoiding the state space explosion of ESTEREL v3 [7]. Hervé Touati brought Com-

puter Aided Design technology in the picture and he showed how to deeply optimized the obtained netlists to make them practical [51]. The author then extended the logic translation to software implementation of general ESTEREL programs. Xavier Fornari extended the hardware optimization techniques to deal with software generation. Frédéric Mignard cleaned up many processors of the ESTEREL V3 compiler and built a bunch of new ones. Jean-Pierre Paris implemented external task control by the exec statement. Jean-Paul Marmorat and Jean-Pierre Paris developed the graphical simulator and symbolic debugger xsimul, which later became the current xes tool. The resulting ESTEREL V4 compiler was delivered in 1992.

ESTEREL V4 was much better than ESTEREL V3 since it avoided state space explosion. However, it required generated circuits to be acyclic. Although this condition is standard in hardware or data-flow systems design, it turned out to be too restrictive for Esterel. The older Esterel v3 compiler was quite smart about causality and was able to compile many correct but cyclic programs that were rejected by the more recent ESTEREL V4 compiler. This made our users unhappy, and we could not convince them that the problem lied in their bad programming habits. On the contrary, they convinced us that making safe cycles is natural when programming symmetric protocols or resource access strategies. The solution came from an encounter with a paper of Sharad Malik on cyclic circuits [38], which we later extended with Tom Shiple [49] by showing the equivalence between three points of views on Boolean circuits: the electrical point of view that deals with current propagation and delays, the constructive logic point of view that deals with proving values of Boolean variables in a constructive way<sup>4</sup>, and the denotational point of view of Scott's semantics. This lead to the constructive semantics presented in [8] and to the current ESTEREL V5 compiler. Technically, the compiling algorithms for the constructive semantics are based on Binary Decision Diagrams. They were implemented by Tom Shiple and Horia Toma with help of Hervé Touati and Jean-Christophe Madre, using the Tiger BDD system of Olivier Coudert, J-C. Madre, and H. Touati. Ellen Sentovich made many contributions to the presentation of the semantics and to optimization techniques, that were developed and implemented by Horia Toma [46, 47]. Xavier Fornari is now in charge of the development of the ESTEREL V5 compiler, which has been heavily tested by Monica Robert.

Synchronous languages are not enough for complex systems programming and they must interact with other languages and communication styles,

<sup>&</sup>lt;sup>4</sup>i.e. without speculative computation or reasoning by contradiction.

in particular with asynchronous ones. The CRP formalism (Communicating Reactive Processes) developed by the author, R.K. Shyamasundar from TIFR Bombay and S. Ramesh from IIT Bombay, India, is an attempt at marrying ESTEREL and CSP. See [26] for a presentation of CRP. The Polis hardware / software codesign system also uses ESTEREL in a mixed synchronous / asynchronous framework. See also [6] for a comparison between synchrony and asynchrony.

The verification tools for ESTEREL are developed by a group headed by Robert de Simone, who also deeply contributed to many aspects of the design of the language and tools. Didier Vergamini developed the early automata manipulation algorithms included in the AUTO explicit verification system, Amar Bouali wrote the current XEVE BDD-based verification package using the TIGER library. Valérie Roy developed the AUTOGRAPH automata visualization tools. Annie Ressouche wrote most of the programs that interface the compiler and the verifiers. These tools are accessible from the ESTEREL Web page. Carlos Puchol, from University of Texas, and Lalita Jagadeesan, from AT&T Bell Laboratories, developed the TEMPEST temporal logic verification system for ESTEREL [35]. Amar Bouali and Valérie Roy replaced the original explicit state enumeration technique by implicit traversal using BDDs in the Hurricane evolution of Tempest.

## Other Synchronous Languages

ESTEREL is a member of a small community of synchronous languages born in the beginning of the 80's. Cooperation has been constant with the Lustre team [30] headed by Paul Caspi and Nicolas Halbwachs in Grenoble, France, and the early ESTEREL and Lustre tools shared intermediate languages and compilation tools. Cooperation was later extended to the Signal [28] team headed by Paul le Guernic and Albert Benveniste in Rennes, France, The design of ESTEREL was influenced by the independent design of the Statecharts visual formalism [32] introduced by David Harel in 1984 and by the Argos synchronous variant of Statecharts developed by Florence Maraninchi in Grenoble [39]. See [29] for a global survey of these synchronous languages.

Charles Andre's SyncCharts [1] graphical formalism is an extension of Argos that yields the power of Esterel. The Modecharts [42] formalism is another synchronous graphical language. The Reactive C language developed by Frédéric Boussinot [17] is a reactive extension of C that borrows its main concepts from synchronous languages and has evolved into

reactive objects languages [19]. Frédéric Boussinot and Robert de Simone also developed a synchronous language called SL [18] that can be viewed as a syntactic restriction of Esterel where all causality problems are suppressed and that can be easily implemented using Reactive C.

### Acknowledgements

Special thanks to Maurice Gherardi, from the Simulog company, who performed a very careful proof-reading and wrote the syntax chapter. Many thanks to Frédéric Boussinot (Ecole des Mines), Sylvan Dissoubray (Simulog) Xavier Fornari (Armines), Emmanuel Ledinot (Dassault Aviation), Eric Nassor (Dassault Aviation), Monica Robert (Armines), and Ellen Sentovich (Cadence) for their proof-reading and numerous improvement suggestions.

Please send report any mistake you find or send any improvement suggestion to berry@cma.inria.fr.

# Chapter 1

# Deterministic Reactive Systems

# 1.1 Transformational, Interactive, and Reactive Systems

Computerized systems can be divided into three broad categories:

- Transformational systems compute output values from inputs values, and then stop. Most numerical computation programs, payroll programs, and compilers are transformational.

- Interactive systems constantly interact with their environment in such a way that the computers can be viewed as the masters of the interaction. A user calls for services, the system listens to him when it can, and it delivers the services when they are available. Operating systems, centralized or distributed databases, and the Internet are interactive.

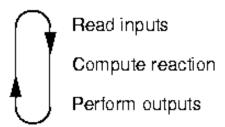

- Reactive systems, also called reflex systems, continuously react to stimuli coming from their environment by sending back other stimuli. Contrarily to interactive systems, reactive systems are purely input-driven and they must react at a pace that is dictated by the environment. Process controllers or signal processors are typical reactive systems.

Of course, a given large-scale computerized system never falls entirely in any of the three categories. A banking system involves transformational payroll programs, interactive access to data bases of clients, and reactive automatic teller machines and graphical user interfaces. Nevertheless, it is always useful to identify which parts of the system are transformational, interactive, or reactive, and to handle them with appropriate tools.

Interactive and reactive systems call for *concurrent programming*. First, they act concurrently with their environment. Second, they are themselves most often made of concurrent parts that communicate with each other, such as the bank and the banker teller in the banking system or the time-keeper, stopwatch, and alarm in a digital watch.

### 1.2 Control-Dominated Reactive Systems

In most reactive applications, there is a fairly clear distinction between data handling and control handling. Data handling is about continuously producing output values from input values. It is the typical activity of signal processing programs. Control handling is about producing discrete output signals from input ones. It is the typical activity of man-machine interface or supervision programs, among other examples listed below. As usual, the two aspects are not fully independent: for instance, in signal processing applications, there are usually several computation modes supervised by some discrete commands. ESTEREL is an imperative concurrent language specifically dedicated to control-dominated (parts of) reactive programs, which are found in the following application areas:

- Real-time process control, in manufacturing, transportation systems, etc. The input stimuli are physical parameters produced by sensors, operator commands, device failure signals, etc. The outputs are commands to motors, valves, etc. The program must react to its inputs within a short predefined time frame. See [4] for the use of Esterel in the Polis hardware / software codesign system.

- Embedded systems that drive automated objects such as robots and domestic appliances. Sequencing tasks is the primary concern. See [25] for examples in robotics.

- Supervision of complex systems, where information coming from a variety of sources is gathered and handled by one or more supervisors, that can be programs, human beings, or a combination of those. Safety systems that detects anomalies in complex processes are typical supervision systems.

- Communication protocols, or more precisely the control part that concerns connection, disconnection, failure recovery, quality of service control, etc. The stimuli are either physical signals sent by line handler devices or logical signals generated by packet decoding. See [13, 43, 35, 36, 22] for examples.

- Peripheral drivers that control disks, printers, or other computer peripherals.

- Hardware glue logic and controllers. Glue logic is a common name for protocols and drivers in hardware design. A typical glue logic device is an interface between two busses. Controllers are finite state machines driving data-paths, usually opening and closing multiplexer according to control conditions. See [7] for examples.

- Human-machine interface. HMI is of course ubiquitous and is a basic tool for supervision. Basic GUIs (Graphical User Interfaces) use a fixed set of predefined interactors such as menubars, scrollbars, etc., see [23]. Modal HMIs fold a lot of commands into a small number of interactors and display a lot of values on a small number of display units. They are very common in industrial systems or in airplane cockpit. See [9] for the small but representative example of a digital wristwatch.

ESTEREL can be used in all these quite diverse domains that are usually handled in different and often separated technical communities. This poses a non-trivial terminology problem, since the same words can have different meanings in different communities, and since the same concepts can be named by different words. In this document, we try to do our best to define all the technical words we use and to relate them to other words used in the different fields whenever necessary.

### 1.3 Determinism Versus Non-Determinism

Determinism vs. non-determinism is a key difference between reactive and interactive systems. A system is said to be deterministic if the same sequence of inputs always produces the same sequence of outputs. It is non-deterministic otherwise.

Determinism is the rule for reactive systems. It is very clear that an airplane must be driven in a deterministic way, and the same holds for

any controlled physical system governed by deterministic physical laws<sup>1</sup>. In man-machine interface systems, it is also clear that user commands have precise deterministic meanings. We leave it for the reader to check that all the aforementioned applications are deterministic.

On the contrary, behavioral non-determinism is the rule for interactive systems for which the interaction is driven by the computers. Even if the Unix kernel is internally deterministic, its scheduling and resource allocation policies are unknown to the user, who naturally perceives the system as non-deterministic: running twice the same sequence of commands can produce different results if there are other interacting users. There should be no need to convince the reader that Internet is and must be non-deterministic.

Non-determinism is much harder to handle than determinism. Non-deterministic systems are harder to specify, and it is not even trivial to define a good notion of behavior and equivalence for them, while execution traces are perfectly adequate for deterministic systems. Debugging non-deterministic systems can be a nightmare since transient bugs may not be reproduced. Analyzing systems is also much more difficult since the state space tends to explode. Therefore, it is important to reserve non-determinism for places where it is really mandatory, i.e. interactive systems, and to forget about it for reactive systems. Historically, it was long thought that concurrency and non-determinism had to go together. As we shall see in the sequel, this is wrong. The main merit of synchronous languages is probably to have reconciled concurrency and determinism.

# 1.4 Programming Tools

We are mostly interested in the programming part of reactive systems, that is, in writing *reactive programs* and making them work. Let us explain why we need specific tools for this purpose.

Transformational systems have been well-studied for very long, since they used to form the bulk of computing. Most programming constructs and languages were originally tailored for them. It is very clear that their extension to event handling in interactive or reactive systems is not obvious: classical languages lack concurrency and event-handling primitives.

Tools for interactive systems programming came afterwards because of the development of operating systems and distributed algorithms. They introduced the key notions of concurrency, communication, and synchronization between processes. In practice, interactive applications are built either

<sup>&</sup>lt;sup>1</sup>more precisely, modeled by deterministic systems of mathematical equations.

by linking conventional transformational programs through synchronizing operating systems calls, or by using specific languages such as CSP [33], OCCAM [34], or ADA [21] that make concurrency and communication first-class citizens. The advantage of specific concurrent languages is clear for program behavior analysis: mathematical semantics can be given in an intrinsic way and proof rules can be derived from it []. Process calculi try to abstract away from the concrete programming issues and to address the essence of interactivity []. Large-scale networking has considerably extended the scope of interactive systems and unveiled new needs such as process migration, realized for example in Milner's  $\pi$ -calculus [] and in the JAVA language [2]

Tools for reactive systems did not develop in the same way. The subject was long kept outside the main core of Computer Science. In our belief, there are three reasons. First, the control and embedded applications used to belong to the domain of control theory and electrical engineering, where the traditions and technical background were quite different<sup>2</sup>. Second, high-level reasoning and programming tools promoted by computer scientists were considered as quite useless by many control engineers, whose main problem was (and still is) to pack code in small ROM for cheap microprocessors. Third, it was long thought by computer scientists that tools designed for interactive systems would cover reactive systems equally well. This turned out to be false, since classical concurrent languages are non-deterministic, give no guarantee about response times, and give no fine control over life and death of reactive activities.

Reactive systems were identified as such in the early 80's by several authors [], the name being given by David Harel and Amir Pnueli. Synchronous languages were born from the recognition that instantaneous broadcasting was the way to handle communication in reactive systems, making it possible to handle together concurrency, determinism, and response time control, and yielding a programming style far more natural than the one enforced by conventional interactive communication mechanisms. Lustre [30], developed by Paul Caspi and Nicolas Halbwachs, is a synchronous functional data-flow language for data-dominated systems. Signal [28] is a powerful relational synchronous data-flow language developed by Paul le Guernic and Albert Benveniste. Statecharts [32] is a visual formalism introduced by David Harel in 1984 for hierarchical state machine design. Argos [39] is a purely synchronous variant of Statecharts developed by Florence Maraninchi. Electre [45] is an imperative task scheduling language that borrows many concepts from synchronous languages. Some of these languages are

<sup>&</sup>lt;sup>2</sup>Even the computers used to be different.

surveyed in a book by Nicolas Halbwachs [29].

All the reactive languages are accompanied by automatic formal verification tools, which are now of common use in industrial environments. It is now recognized that *safety* is the main concern in reactive systems. This is why rigorous high-level languages and verification tools will gradually replace low-level hand programming and testing, as in all the other areas of Computer Science. Formal verification issues will not be covered in this language primer, see [] for more information.

As of now, there is no completely satisfactory way of unifying the dataflow styles of LUSTRE and SIGNAL and the control flow styles of ESTEREL and STATECHARTS. The programming primitives one need for data-handling and control-handling are indeed quite different. This is somewhat unfortunate for the user. Research is active in this area, and we hope to come up with a reasonable theoretical and practical unification in a finite amount of time.

We mentioned that classical concurrent languages were inadequate for reactive programming. The converse is also true: reactive languages are largely inadequate for interactive programming as a whole, although they can be locally useful for reactive parts of interactive programs. Here also, there is no known way to unify the interactive and reactive styles <sup>3</sup>. A nice pragmatic superposition of both approaches could be the network of reactive objects studied for example in [].

<sup>&</sup>lt;sup>3</sup>In [5], we claim that reactive programming is akin to Newtonian mechanics while interactive programming is akin to chemistry. We shall not develop the argument here, but just remind the reader that there is no physical theory that unifies in a simple way mechanics and chemistry.

# Chapter 2

# The Esterel Programming Style

## 2.1 Pure Signal Handling: the ABRO example

Our first example is the following specification:

Specification ABRO:

Emit an output O as soon as two inputs A and B have occurred. Reset this behavior each time the input R occurs.

The ABRO specification can be implemented either in hardware or in software. We first assume that the implementation is to be done by a synchronous digital circuit, because circuits have the simplest timing model to start with. Software implementation of the same program will be explained later on.

The interface of a (sequential) digital circuit is defined by a list of input wires, a list of output wires, and a clock. In the electrical view, the wires carry voltages, say 0V and 3.3V, and the clock tells when outputs can be sampled and when values can be latched in registers. In terms of clock cycles, registers behave as unit-delay elements. In the logical view, the wires carry Booleans values and the clock determines the successive reactions instants. The logical values are called 0 and 1, or true and false, or set and unset, or present and absent, according to local usage. In ESTEREL, we use present and absent, reserving 0 and 1 for integers and true and false for Boolean data. Presence or absence defines the status of a signal. In the ABRO specification, we say that signals occur, which is the same as saying that they are present.

An *input event* is defined by a status for each input. Given an input event, the circuit computes an *output event* made of a status for each output. A new input event is processed at each clock cycle.

Being carried by independent wires, hardware input signals can be simultaneously present in the same clock cycle. The ABRO specification is actually ambiguous, because it does not talk about handling such simultaneous occurrences of signals. There is clearly no problem if A and B are simultaneously present: O must be emitted right away. What if A and B are present when R occurs? We assume that R takes priority and that A and B are ignored when R occurs. Other choices will be studied later on. There is also another minor ambiguity at *boot time*, i.e. for the initial transition. Here, we assume that booting ABRO is a blank step and that the real behavior starts only after boot. This is a common assumption.

#### 2.1.1 Execution Traces

It is convenient to have a notation for execution traces of a specification or program. We use that of the ESTEREL V5 csimul simulator. Here is a correct trace w.r.t. the ABRO specification:

```

> ;

Output:

> A;

Output:

> B;

Output: O

> R;

Output:

> A B;

Output: O

> ;

Output: > A B R;

Output:

```

A trace is an alternated sequence of *reactions*, each reaction being composed of an input event preceded by the prompt '>' and an output event preceded by 'Output:'. An input event is written as the list of present signals terminated by a semicolon. Only the present or *emitted* output signals are mentioned in the output list; for controller programming, the main goal of ESTEREL, this is usually economical since control signals tend to be more

often absent than present. A blank event is one with no signal mentioned, i.e. one where all signals are absent. Here, the initial (boot) input event is blank and there is another blank input event before the second reset. The response to this event is a blank output event.

The trace notation implicitly defines the basic timing model. Time is logical and seen as generated by the sequence of reactions, also called *instants* or *ticks*, which directly correspond to hardware clock cycles. We say that a reaction occurs at time t if its rank in the trace is t. With that timing notion, the output part of an event occurs at the same logical time as the input: only bookkeeping actions are performed in a reaction, and such actions should not consume logical input time. This model is called the perfectly synchronous or *zero delay* model. It will be analyzed in depth in Chapter 5.

#### 2.1.2 Mealy Machines

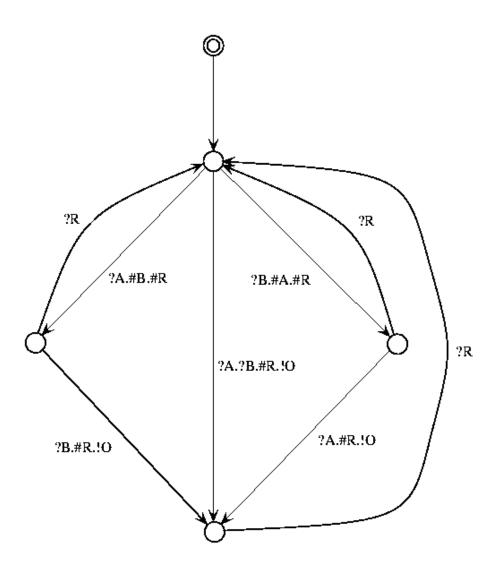

A common way of programming ABRO is to design a deterministic *Mealy machine* (in state graph form), which is a deterministic finite automaton in which each transition arrow bears an input / output label. A Mealy machine for ABRO is pictured in Figure 2.1. A transition label contains input signals preceded by either '?' for presence or '#' for absence and output signals preceded by '!'. A transition labeled "?A.#B.!O" is taken if A is present and B is absent in the input event, and it provokes emission of O. A label acts as a filter for input events. In "?A.#R.!O", the transition is taken if A is present, independently of the presence of B. In other words, a transition labeled "?A.#R.!O" abbreviates the pair of transitions "?A.?B.#R.!O" and "?A.#B.#R.!O".

Notice that a Mealy machine can be seen as a folding of all possible traces into a single graph, sharing states with identical futures. Hardware can be automatically synthesized from Mealy machine specifications.

### 2.1.3 ABRO in Esterel

Since we have Mealy machines, why should we bother building new languages? Look at the automaton in Figure 2.1. Each signal appears several times, unlike in the original specification. For example, A appears 3 times positively: once on the left, as the first input, once on the right, as the second input, and once in the middle, for the case where A and B are simultaneous. It also appears negatively on the right. The reset signal R appears 8 times, 3 times positively and 5 times negatively. The output O also appears 3 times, one for each possible sequencing of A and B. Consider now the prob-

Figure 2.1: The ABRO Mealy machine

lem ABCRO, where there is one more signal C to wait for before emitting O. We leave the automaton drawing to the reader: the automaton core now has the shape of a 3-D cube with 8 vertices. Of course, the n-signal problem yields a n-cube with  $2^n$  vertices. This is not for human beings. Furthermore, automata are hard to draw and read if not ridiculously small, and they are very sensitive to specification changes. In practice, Mealy machines are in no way good programs. In contrast, the ESTEREL code for ABRO is:

```

module ABRO:

input A, B, R;

output O;

loop

[await A || await B ];

emit O

each R

end module

```

The declaration part is trivial. The body is written in an imperative way using control threads. It involves five ingredients: delay, signal emission, sequencing, concurrency, and abortion. It can be read either in an outside-in way, insisting first on the reset aspects, or in an inside-out way, insisting first in the basic behavior. We choose the inside-out way for this example.

ESTEREL statements are imperative. A statement starts in some instant t, remains active for a while, and may terminate in some instant  $t' \geq t$ . A statement is instantaneous if t' = t; hardware designers would say that the statement is combinational. If t' > t, we say that the statements takes time; hardware designers would say that the statement is sequential.

The delay statement "await A" always takes time; it *lasts one* A: if started at time t, it terminates at the least t' > t such that A occurs at t', staying active in between. In terms of threads, the current control thread is stuck at the await statement until A occurs.

In "await A  $\mid \mid$  await B", the parallel bars denotes explicit concurrency. When a parallel statement  $p \mid \mid q$  starts, it instantaneously starts its branches p and q, thus forking its incoming control thread. Here, both await statements start simultaneously and instantaneously when the parallel starts. The threads then evolve in lockstep compared to the environment: in each instant, each of them reacts to the current input event. Here, the processing is trivial: the first branch tests for A in each instant and terminates when A occurs, while the second one tests for B and terminates when B occurs. The parallel statement performs branch synchronization by terminating in the precise instant where both branches are terminated. The branches need not

terminate at the same time, the parallel waiting for the last one. Therefore, our parallel terminates exactly when both  $\mathtt A$  and  $\mathtt B$  have been received, be they successive or simultaneous.

The brackets '[' and ']' are statement parenthesis used to solve syntactic priority conflicts. They are necessary here since the *sequencing* operator ';' binds tighter than the parallel operator ' $|\cdot|$ '. Sequencing is as usual. In a sequence "p; q", the statement q starts when p terminates. However, in ESTEREL, sequencing is instantaneous: q starts in the instant where p terminates; there is no reason to consume logical time for trivial bookkeeping.

The "emit 0" statement is instantaneous. It emits the signal 0 and terminates at the time it starts. Therefore, 0 is emitted exactly at the time where the last of A and B occurs, which is the best meaning we can give to the "as soon as" specification.

The last item is the handling of the reset condition by the abortion loop "loop p each R". The semantics is as follows. When the loop starts, it starts instantaneously its body p. The body runs freely until the next occurrence of R. At that time, the body is aborted if still active and it is immediately restarted afresh. If the body terminates before R occurs, one simply waits for R and restarts the body afresh. Abortion is strong: the active body of the "loop...each" statement does not receive control at abortion time to react from its current state, which is ignored and discarded. It is only restarted afresh.

Using strong abortion, signal priority is simply realized by statement nesting: the outermost abortion by R takes priority over the innermost delays waiting for A and B that are not watched for when R occurs. Therefore, priority is handled by structure, not by artifacts such as explicit numerical indices. Abortion is a strong form of statement *preemption*. A milder form of preemption called *suspension* will be presented in Section 2.6.

The Esterel code for ABCRO is

```

loop

[ await A || await B || await C ];

emit O

each R

```

The code grows linearly with the size of the specification.

# 2.2 Write Things Once

The ABRO example illustrates the fundamental difference between Mealy machines and ESTEREL programs. Esterel statements make it possible to re-

place replication by structure. This is the essence of language design: loops, functions, concurrency, objects, etc. all replace explicit code replication by structure. The real key to good programming is the Write Things Once or WTO principle: any violation of this principle means a replication that makes the program harder to understand and to maintain, and yields a potential source of bugs: modifying a copy without modifying the other ones. We do not claim that ESTEREL fully achieves WTO. We only claim that the ESTEREL primitives help finding the real structure of reactive applications, which is the prerequisite to WTO.

In ABRO, each construct contributes in its own way to WTO. Concurrency immediately saves an exponential. Sequencing is fundamental for using a single occurrence of 0 for all the termination cases of the parallel statement. The "loop...each" abortion statement makes it possible to preempt the body in any state using a single occurrence of R. All these constructs are *orthogonal*. This means that they can be freely mixed at any nesting depth without restriction. Here, the parallel statement appears within a sequence that itself appears within an abortion. Many languages limit concurrency to toplevel, therefore loosing orthogonality. This is a sure way of not achieving WTO.

Communication in ESTEREL is done by *broadcasting*. Input broadcasting was implicit when we said that concurrent statements evolve in lockstep in the same input environment. Broadcasting is extended to all signals. For examples, processes interested in knowing when ABRO emits O just wait for O. They do not have to signal their identity to ABRO, the code of which does not depend on the number of receivers. Broadcasting is essential for WTO in reactive systems programming.

There are other ways to obtain similar results. An important one is the definition of hierarchical automata in Statecharts [32], Argos [39, 29], or Synccharts [1]. All these formalisms extend Mealy machine in a fully compatible way and use broadcasting, achieving WTO up to some extent. Their compilers are able to re-generate flat machines from structured source code (for Esterel v5, use the -A automaton code generation option).

# 2.3 Valued signals: the SPEED example

The next example is more on the software side, although it can obviously be implemented in hardware. It is used for bicycles, cars, etc.

Specification SPEED:

Count the number of centimeters run per second, and broadcast that number as the value of a Speed signal every second.

We assume that centimeters and seconds are received as discrete ticks of signals Centimeter and Second. The specification is somewhat ambiguous if Centimeter and Second can be simultaneous. Unlike for ABRO, we first neglect this case, assuming that our execution environment (operating system) does not support input event simultaneity, i.e. that it serializes the events it sees. This assumption is very common is event-queue based reactive software design.

The ESTEREL implementation uses a *valued signal* to broadcast the speed. In addition to its presence status, a valued signal carries a value, which can be of arbitrary type. Let us stick to primitive type **integer** for the time being. The code of **Speed** is:

```

module SPEED:

input Centimeter, Second;

relation Centimeter # Second;

output Speed : integer;

loop

var Distance := 0 : integer in

abort

every Centimeter do

Distance := Distance+1

end every

when Second do

emit Speed(Distance)

end abort

end var

end loop

end module

```

In the declaration part, the relation declaration declares the Centimeter and Second input signals to be exclusive, using the '#' symbol, which is the way to assert input serialization. The declaration of Speed declares this signal to be of type integer.

Let us read the executable body in an outside-in way. The "loop...end" statement performs an infinite loop, restarting its own body afresh as soon as it terminates. The var keyword declares a local variable called Distance, of type integer, initialized to 0.

The abort statement preempts its body when the Second signal occurs. An abort statement can have a timeout clause following the 'do' keyword. Here, the timeout clause emits the speed; in general, it can be an arbitrary statement. The body of the abort statement is an every temporal loop that increments the Distance variable every centimeter. The incrementation is instantaneous (or, as before, the incrementation time is neglected compared to the input time).

The every statement differs from the loop...each statement presented in Section 2.1.3 at initialization time. In "loop p each S", the body p is started right away. In "every S do p end", one waits for the first occurrence of S to start p. The every statement could be written

```

await S; loop p each S

```

Although not primitive, the every statement is necessary to avoid duplicating S and to achieve WTO.

Since control transmission and arithmetic operations are instantaneous, the speed is emitted right away when a second occurs: this is the only way to respect the mathematical definition of the speed, which would be broken by any extra delay. In ESTEREL, when we write Speed, we mean speed!

### 2.3.1 Valued Signals Versus Variables

The body of SPEED uses a variable Distance to compute the value of the speed. Variables and signals are very different objects.

• A signal is shared throughout its scope, which is the whole program for an interface signal and the scope of its declaration for a local signal, see Section 2.5. A valued signal has one and only one status and one and only one value at a time. Both the status and the value are broadcast. Unlike the status, the value is permanent; if it is unchanged in an instant, the value is that of the previous instant. The writers of a signal are the environment for an input signal and the emit statements for an output or local signal. The value can be changed only when the status is present. The readers are the presence or preemption tests for the status, and the value access expression '?S' for the value. Presence tests and value access expressions can occur anywhere in the signal's scope.

- A variable is local to a thread in case the thread writes it. Its value is written by an instantaneous assignment statement<sup>1</sup>. The value is read in expressions when the variable's identifier is mentioned, as usual. If the thread forks on a "||" parallel statement, then only two cases are legal:

- The variable is accessed in read-only mode in each subthread,

- If the variable is written by some thread, then it can neither be read nor be written by concurrent threads.

Unlike a signal, a variable can take several successive values in an instant. For example, in SPEED, the Distance variable takes two successive values in the same instant when a centimeter occurs: if its value is n before the assignment, it is n+1 after the assignment. The order in which the values are taken is the internal control-flow order of the program, which we shall call the constructive order in Chapter 4.2. For the control-flow order to be well-defined, it is forbidden to write concurrent assignments such as

```

X:=0;

X:= X+1

||

X:= 1

```

There is no way to give decent meaning to such a construct in a synchronous deterministic framework.

For a signal, it is possible and sometimes useful to write simultaneous concurrent emissions such as "emit S(1) || emit S(2)", using an associative and commutative function to combine the emitted values. The discussion of this feature is deferred to Section 3.4.

For a valued signal, it is impossible to use the signal's value in its own computation, unlike for a variable. A frequent beginner's mistake is to write

```

emit S(?S+1)

```

to increment the current value of a signal S. This does not work, since the current value ?S of S is precisely the one emitted by the emit statement. The value should satisfy the equation ?S = ?S + 1, which is impossible. This phenomenon is called a *causality cycle*. It is analyzed in Section 4.2.

<sup>&</sup>lt;sup>1</sup>Or by an instantaneous external procedure call, see Section 3.3.4, or by a non-instantaneous exec remote task execution statements, see Section 3.7.16.

In ESTEREL, a signal-variable pair and an assignment are needed to compute the new signal value, as for Speed above. Lustre and Signal are more clever, since they allow the user to refer to the *previous* value of a signal. One could indeed safely write

```

emit S(?pre(S)+1)

```

but this is not yet available in Esterel.

### 2.4 Weak and Immediate Abortion

Let us now accept simultaneity of Centimeter and Second, which is natural for an hardware implementation and can also be considered useful for a software implementation. For example, in a polling implementation, the module is called at regular time intervals with the inputs buffered since last call. Then, Centimeter and Second are seen as simultaneous if they are close enough.

What should we do if a centimeter and a second occur simultaneously? The centimeter can be considered as belonging either to the second interval that ends in the current instant or to the one that starts in the current instant, the choice belonging to the specifier. Here, we show how to implement both choices. Beforehand, we need to refine the semantics description of delays and abortion. For "abort p when S", the exact behavior is as follows:

- In the starting instant, p is immediately started, the initial presence or absence of S being ignored.

- If p terminates before S occurs, then the whole abort statement terminates at the same time.

- If S occurs while p is not yet terminated, then the abort statement immediately terminates and p does not receive the control in the current instant.

Because of the first and third clauses respectively, we say that the abort statement is *delayed* and *strong*. It is clear that we may need different behaviors in the first and last instant. To make the abort statement sensitive to S in the first instant, we add the immediate keyword in the delay specification:

```

\begin{array}{c} {\rm abort} \\ p \\ {\rm when \ immediate \ S} \end{array}

```

Then, an occurrence of S in the first instant provokes an immediate termination of the abort statement, without p being started at all.

To make the body have its "last wills" and receive the control for a last time at abortion time, we add the weak keyword:

```

\begin{array}{c} \text{weak abort} \\ p \\ \text{when S} \end{array}

```

If p is non-instantaneous and if S occurs before p terminates, then the weak abort statement is terminated instantaneously as usual but p receives the control for a last time when S occurs. Here, the abort statement is delayed and an initial S is ignored.

If we want to take an initial S into account as well, we use both the immediate and weak keywords:

```

\begin{array}{c} \text{weak abort} \\ p \\ \text{when immediate S} \end{array}

```

Then, if S occurs in the starting instant, the statement terminates but p is executed in the instant. The four possible cases are now covered.

The every statement performs strong abortion of its body and it is delayed by default. The statement "every S do p end" is actually not a primitive statement, but an abbreviation for

```

await S;

loop

abort

p; halt

when S

end loop

```

where the halt primitive statement waits forever. The loop abbreviates the "loop...each" statement. The every statement also has an immediate form, written

```

every immediate S do p end

```

In the expansion, the initial await statement is made immediate<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>We do not allow weak every, which never proved that useful, but this is a lack of orthogonality that might be corrected some day.

Back to our SPEED problem, what happens if we simply remove the relation in the initial coding of SPEED? Well, things go wrong. Consider an instant where Centimeter and Second both occur. Since the abortion by Second is strong, the internal every statement is not executed, which implies that Centimeter is not counted in the currently finishing second. The external loop loops and the every statement is instantaneously restarted. Since it is a delayed every, the current centimeter is not taken into account either. Therefore, the centimeter is lost.

Let us now code the two possible consistent specifications. First, assume we want to count the centimeter in the finishing second. We just make the abort statement weak:

```

loop

var Distance := 0 : integer in

weak abort

every Centimeter do

Distance := Distance+1

end every

when Second do

emit Speed(Distance)

end abort

end var

end loop

```

The "every Centimeter" statement is now executed if the two inputs are simultaneous, and the distance is incremented before the speed is emitted. Here, "before" refers to control propagation in threads. When the external loop loops, control reaches the "every Centimeter" statement again, which ignores the current centimeter since it is delayed.

To count the centimeter in the next second, we leave the abort strong and we make the every immediate:

```

loop

var Distance := 0 : integer in

abort

every immediate Centimeter do

Distance := Distance+1

end every

when Second do

emit Speed(Distance)

end abort

end var

end loop

```

Then the centimeter is not counted in the finishing second interval but it is counted in the now starting interval since the immediate every statement executes its body.

Finally, notice that making both the await statement weak and the every statement immediate would lead to count the centimeter *twice*, another possible mistake<sup>3</sup>.

Back to the ABRO example of Section 2.1, assume now that R should not take priority over A and B any more and that O must be emitted even if R occurs. This behavior can be coded by replacing the abort statement implicit in loop...each by weak abort:

```

loop

weak abort

[await A || await B];

emit O;

halt

when R

end loop

```

## 2.5 Using Submodules: the REGUL Specification

Consider now the following specification of part of a car speed regulation system:

#### Specification REGUL:

In each instant, emit the result of the function Regfun applied to the position of the gas pedal and the current speed as the value of the Regul signal.

Of course, the emission of Regul should start only once the first value of Speed has been computed. For REGUL, we additionally require the implementation to reuse the SPEED module.

Here, we mention a function called Regfun. Such an object is external to ESTEREL and written in the *host language* in which the ESTEREL program will be compiled, for example C. The code of REGUL is:

<sup>&</sup>lt;sup>3</sup>These problems make the author remember the elementary school fencepost problems ( $problèmes\ de\ poteaux$ , in French): if a fence has n poles, how much wire should I buy? It terribly depends on the shape of the fence. Although there is apparently no more open problems in the field, it is still one of the most difficult part of engineering.

```

module REGUL:

function Regfun (integer, integer) : integer;

input Centimeter, Second;

sensor GasPedal : integer;

relation Centimeter # Second;

output Regul : integer;

signal Speed : integer in

run SPEED

||

await Speed;

sustain Regul(Regfun(?Speed, ?GasPedal))

end signal

end module

```

We first declare the type of the external Regul function, which is necessary for type-checking. We then declare GasPedal to be a sensor. A sensor is a valued signal without the presence status part. A gas pedal or a thermometer usually do not send interrupts, they just define numerical values that can be read at any time. For them, the status part is useless (equivalently, the status is always present). The value of a sensor is read by the '?' operator, just as for valued signals.

The body is a local signal declaration that declares the Speed local signal and whose own body is made of two parallel statements. The first statement is an instantiation of the SPEED module using the run keyword, which amounts to copying its body in place and binding the interface signals of SPEED to the signals bearing the same name in the instantiation scope. The second statement is the sequence of an "await Speed" delay and of a sustain statement that emits the Regul signal with the required difference value in each instant, unlike the emit statement that works only once. The Speed local signal is generated by the SPEED module. It is instantaneously broadcast to all statements in its scope. Therefore, it is received by the sustain statement at the time where it is generated, which ensures that the value of the Regul signal is always exactly the required one. The "await Speed" delay is necessary to ensure that the value of the Speed signal is well-defined when the value of Regul is computed. Before the first emission of Speed by SPEED, the value ?Speed is undefined.

## 2.6 Suspension

We now present *suspension*, which is a mild form of instantaneous preemption. In Unix, typing ^C aborts a process, while typing ^Z suspends it; the

suspended process is resumed when typing bg or fg. The ESTEREL suspend statement realizes a similar function. However, instead of using a ^Z-fg suspend-resume mechanism, suspension is determined in each instant by the presence of a signal.

Assume the speed regulation system should be suspended when the user keeps the Coast button pressed. This means that the Regul signal should not be emitted if the Coast signal is present. This goal is achieved by replacing the sustain statement by the following construct in the body of REGUL:

```

suspend

sustain Regul(Regfun(?Speed, ?GasPedal))

when Coast

```

In this simple case, the body of the **suspend** statement has only one state. In the general case, one can suspend an arbitrary statement in any of its state. The state is frozen until next instant.

Suspension by suspend is delayed, just as abortion by abort: in the starting instant, the presence of the suspension signal is not tested for and the body is run anyway. Suspension can also be made immediate, as in

```

suspend

sustain Regul(Regfun(?Speed, ?GasPedal))

when immediate Coast

```

The regulation user interface may be different, involving for example a CoastOn-CoastOff button pair with CoastOn # CoastOff, which calls for a suspend-resume way of doing things. In ESTEREL, this is easily done by synthesizing the Coast signal from CoastOn and CoastOff:

```

signal Coast in

suspend

sustain Regul(Regfun(?Speed, ?GasPedal))

when Coast

||

loop

await CoastOn;

abort

sustain Coast

when CoastOff

end loop

end signal

```

#### 2.7 Generic Behaviors and Modules

In the previous coasting example, the loop in the second branch of the parallel statement implements a very common two-states behavior. Therefore, to achieve WTO, it is useful to make a generic module for that behavior. For this, we just build a module with standard names for interface signals:

```

module TWO_STATES:

input On, Off;

output IsOn, IsOff;

loop

abort

sustain IsOff

when On;

abort

sustain IsOn

when Off

end loop

end module

```

Then the module can be instantiated as follows in place of the original loop:

Explicit renaming using the '/' symbol overrides the default signal capture by name. The dummy declaration of the unused signal IsOff is necessary since IsOff is declared in TWO\_STATES and must be bound to a signal in the caller. Notice that IsOff is captured by name since it does not appear in the renaming list.

An interesting way to program the ABCRO specification of Section 2.1 is to consider ABRO as a generic behavior to be reused twice in parallel:

```

module ABCRO:

input A, B, C, R;

output O;

signal AB in

run ABRO [ signal AB / O]

||

run ABRO [ signal AB / A, C / B]

end signal

end module

```

Notice that R will reset the two submodules simultaneously, thanks to the synchronous model.

The SPEED module should also be made generic, actually in a much broader sense. To measure the speed, it does not matter whether we count centimeters per second, meters per hour, or whatever. It does not matter either whether the speed type is integer, float, or whatever. The type, the initial value, the incrementation function, and the signals should be passed as parameters. In ESTEREL, the generic code is:

```

module GENERIC_SPEED;

type T;

constant Initial: T,

Increment : T;

function Add (T, T) : T;

input A, B; % count how many A's per B

output Speed : T;

loop

var NumberOfA := Initial : T in

abort

every immediate A do

NumberOfA := Add(NumberOfA, Increment)

end

when B do

emit Speed(NumberOfA)

end abort

end var

end loop

end module

```

The original SPEED module can be obtained by instantiating GENERIC\_SPEED as follows:

The run statement is conceptually replaced by the body of GENERIC\_SPEED with the appropriate substitutions done. For example, the actual value 0 is substituted to the Initial constant. Renaming arguments are passed by name and not by position as in LUSTRE or SIGNAL. Each technique has its advantages and drawbacks. Passing by name can be heavier, but passing by position is messy for long argument lists that often occur in practice. Moreover, we can use a very convenient abbreviation: if a name is kept unchanged in a substitution, we just don't mention it. This is what we did for REGUL, see Section 2.5. Finally, it is also possible to give another name to an instantiated submodule, see Section 3.7.15.

## 2.8 Multiform Time

In ESTEREL, there is no predefined time unit and Second or Millisecond act as standard signals. Conversely, any signal can be considered as defining an independent time unit, which gives a broader meaning to timing control issues. Consider the following elementary school reactive problem:

You are driving your car at 100 km/h. Suddenly, you see an obstacle on the road at a distance of 50 m. Your reflex time is 1/10 s. Your brakes are able to decelerate the car at 5 m/s<sup>2</sup>. What is your timing constraint?

The right answer is 50 meter. This is indeed the only thing that matters to avoid hitting the obstacle. Read the question carefully: it is not "Will you hit the obstacle", which is a different much more difficult issue related to program verification. That issue can actually be rephrased as the generic sentence "Will you meet your timing constraint?". In ESTEREL, we want to express timing constraints, not necessarily to check them.

Using meters as "timing constraints" may look unconventional. We consider time as being multiform: the repetition of any signal can be considered as defining its own time measure. Signal periodicity may be of interest for physical modeling, but not for programming. Programming in ESTEREL mostly consists in understanding what are the time units of a problem and how they relate with each other. In SPEED, we measure the speed in the usual unit, centimeters per second. In some applications, it might be better to use the inverse of the speed expressed in seconds per centimeter. It is fundamental to understand that this quantity is computed by the very same program. Passing Centimeter for A and Second for B in GENERIC\_SPEED

yields the speed, passing Second for A and Centimeter for B yields the inverse of the speed.

## 2.8.1 The RUNNER example

The next RUNNER example makes heavy use of multiform time.

#### Specification RUNNER:

Every morning, go the stadium and do the following for a fixed number of laps: walk for 100 meter, then, during 15 seconds, keep jumping at each step; finish the lap by running full speed.

The inputs are Second, Morning (synchronous with Second), Meter, Step, and Lap (synchronous with Meter). The current action is determined by an output signal chosen among Walk, Jump, and Run. The Walk and Run signals must be continuously emitted, while the Jump signal should only be sent in response to a Step input. The code is as follows:

```

module RUNNER:

constant NumberOfLaps : integer;

input Morning, Second, Meter, Step, Lap;

relation Morning => Second,

Lap => Meter;

output Walk, Jump, Run;

every Morning do

repeat NumberOfLaps times

abort

abort

sustain Walk

when 100 Meter;

abort

every Step do

emit Jump

end every

when 15 Second;

sustain Run

when Lap

end repeat

end every

end module

```

The code is self-explanatory and it means exactly what it says. The implication relations written using the '=>' symbol express synchrony of Morning with Second and of Lap with Meter. Notice the following facts:

- If a lap is shorter than 100 meter, the runner will keep walking during that lap; the length of successive laps is not bound to be constant.

- If a lap is shorter than (i.e. occurs before) 100 meter plus 15 seconds, then the runner will never run during that lap.

provided of course that mornings do not occur too often compared to meters, seconds, and laps.

The same program written in an asynchronous language would have a quite different meaning. For example, there could be in principle any physical delay between the time a lap is ended and the Lap signal is actually perceived by the program. This is why asynchronous languages cannot handle reactive specifications.

# 2.9 Traps and Exception Handling

Let us add an extra specification item to REGUL: if the speed gets bigger than a constant MaxSpeed, the behavior should be stopped at once and an alarm should be emitted. This is programmed using the trap construct:

```

trap SpeedTooHigh in

signal Speed: integer in

run SPEED

\prod

await Speed;

sustain Regul(Regfun(?Speed, ?GasPedal))

П

every Speed do

if ?Speed > MaxSpeed then

exit SpeedTooHigh

end

end every

end signal

handle SpeedToHigh do

emit Alarm

end trap

```

The if statement instantaneously tests its Boolean condition. If the condition is true, the then clause is instantaneously executed. Here, it is an exit statement. When such a statement is executed, control is instantaneously transferred to the corresponding handler if there is one, the trap simply terminating if there is no handler. At exit time, all statements in the trap body are weakly aborted, as for a weak abort statement (weak abort is actually a macro-statement built using traps).

Similarly, for the runner, the jumping phase is pretty strenuous. During that phase, one should monitor the heart and rush to hospital if there is any problem. The program structure is

```

every Morning do

trap HeartAttack in

repeat NumberOfLaps times

abort

abort

sustain Walk

when 100 Meter;

abort

every Step do

emit Jump

end every

\Pi

<MonitorHeart>

when 15 Second;

sustain Run

each Lap

end repeat

handle HeartAttack do

<RushToHospital>

end trap

end every

```

We leave it to the reader to fill in the details, i.e. to write the program fragments <MonitorHeart> that contains the "exit HeartAttack" statement and <RushToHospital>. In the way we wrote the program, the runner may have to rush to the hospital every morning. Swapping "every Morning" and "trap HeartAttack" would yield a different behavior: at first heart attack, the runner would abandon running for good.

# 2.10 Boolean Signal Expressions and the Present Test

So far, we have handled signals only by using preemption constructs. It is also useful to perform instantaneous presence tests of signals using the dedicated **present** statement. We give three examples of such tests.

Consider first the TWO\_STATES module of Section 2.7. In this module, we clearly start in the off state. In practice, it is also useful to be able to start in the on state. One way of doing that is to invert on and off states at module instantiation time, writing for example

This is quite clever, but probably a little bit too clever and somewhat misleading. A more pedestrian way is to use another signal meaningful only at module start time to determine in which state to start:

```

module TWO_STATES:

input StartOn;

input On, Off;

output IsOn, isOff;

loop

present StartOn else

abort

sustain IsOff

when On;

end present;

abort

sustain IsOn

when Off

end loop

end module

```

If StartOn is present, we skip the off state and start directly in the on state. Notice that the then clause of the present test is omitted; if StartOn is present, the present statement simply terminates, otherwise the else branch is immediately started. If one finds the omission of then misleading, one can write the test as follows:

```

present [not StartOn] then ...

```

To use the module with initial state the on state, just write

```

signal StartOn in

emit StartOn;

run TWO_STATES [...]

end signal

```

Remove the emit statement to start in off mode.